#### SCAN90CP02

# 1.5 Gbps 2x2 LVDS Crosspoint Switch with Pre-Emphasis and IEEE 1149.6

#### **General Description**

The SCAN90CP02 is a 1.5 Gbps 2 x 2 LVDS crosspoint switch. High speed data paths and flow-through pinout minimize internal device jitter, while configurable 0/25/50/100% pre-emphasis overcomes external ISI jitter effects of lossy backplanes and cables. The differential inputs interface to LVDS and Bus LVDS signals such as those on National's 10-, 16-, and 18- bit Bus LVDS SerDes, as well as CML and LVPECL. The SCAN90CP02 can also be used with ASICs and FPGAs. The non-blocking crosspoint architecture is pinconfigurable as a 1:2 clock or data splitter, 2:1 redundancy mux, crossover function, or dual buffer for signal booster and stub hider applications.

Integrated IEEE 1149.1 (JTAG) and 1149.6 circuitry supports testability of both single-ended LVTTL/CMOS and differential LVDS PCB interconnect. The 3.3V supply, CMOS process, and LVDS I/O ensure high performance at low power over the entire industrial -40 to +85°C temperature range.

#### **Features**

- 1.5 Gbps per channel

- Low power: 70 mA in dual repeater mode @1.5 Gbps

- Low output jitter

- Configurable 0/25/50/100% pre-emphasis drives lossy backplanes and cables

- Non-blocking architecture allows 1:2 splitter, 2:1 mux, crossover, and dual buffer configurations

- Flow-through pinout

- LVDS/BLVDS/CML/LVPECL inputs, LVDS Outputs

- IEEE 1149.1 and 1149.6 compliant

- Single 3.3V supply

- Separate control of inputs and outputs allows for power savings

- Industrial -40 to +85°C temperature range

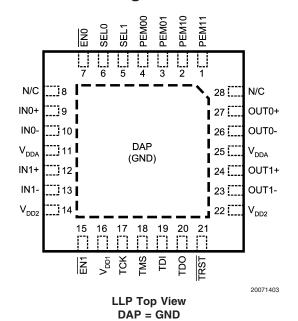

- 28-lead LLP package, or 32-lead LQFP package

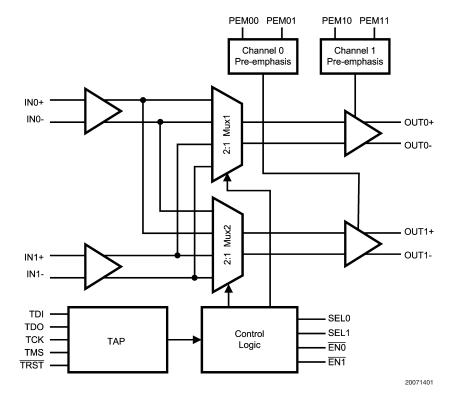

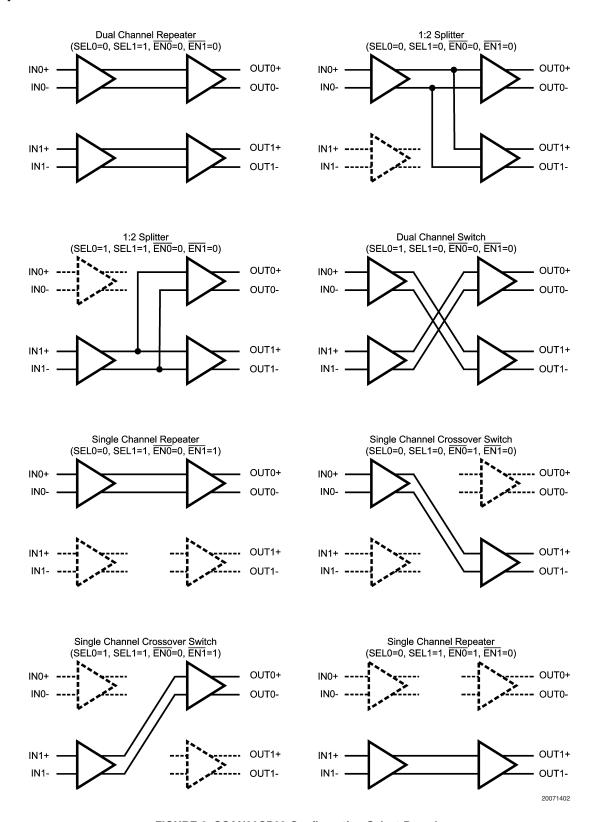

#### **Block Diagram**

FIGURE 1. SCAN90CP02 Block Diagram

# **Pin Descriptions**

| Pin<br>Name | LLP Pin<br>Number | LQFP<br>Pin<br>Number | I/O, Type     | Description                                                                     |  |  |  |

|-------------|-------------------|-----------------------|---------------|---------------------------------------------------------------------------------|--|--|--|

| DIFFERE     | NTIAL INP         | UTS COM               | ION TO ALL MU | XES                                                                             |  |  |  |

| IN0+        | 9                 | 9                     | I, LVDS       | Inverting and non-inverting differential inputs. LVDS, Bus LVDS, CML, or        |  |  |  |

| INO-        | 10                | 10                    |               | LVPECL compatible.                                                              |  |  |  |

| IN1+        | 12                | 13                    | I, LVDS       | Inverting and non-inverting differential inputs. LVDS, Bus LVDS, CML, or        |  |  |  |

| IN1-        | 13                | 14                    |               | LVPECL compatible.                                                              |  |  |  |

|             | D DIFFER          | ENTIAL OL             | JTPUTS        |                                                                                 |  |  |  |

| OUT0+       | 27                | 32                    | O, LVDS       | Inverting and non-inverting differential outputs. OUT0± can be connected to any |  |  |  |

| OUT0-       | 26                | 31                    |               | one pair IN0±, or IN1±. LVDS compatible (Note 2).                               |  |  |  |

| OUT1+       | 24                | 28                    | O, LVDS       | Inverting and non-inverting differential outputs. OUT1± can be connected to any |  |  |  |

| OUT1-       | 23                | 27                    |               | one pair IN0±, or IN1±. LVDS compatible (Note 2).                               |  |  |  |

|             | CONTROL           | INTERFAC              | E             |                                                                                 |  |  |  |

| SEL0,       | 6                 | 7                     | I, LVTTL      | Select Control Inputs                                                           |  |  |  |

| SEL1        | 5                 | 6                     |               |                                                                                 |  |  |  |

| ENO,        | 7                 | 8                     | I, LVTTL      | Output Enable Inputs                                                            |  |  |  |

| EN1         | 15                | 17                    |               |                                                                                 |  |  |  |

| PEM00,      | 4                 | 4                     | I, LVTTL      | Channel 0 Output Pre-emphasis Control Inputs                                    |  |  |  |

| PEM01       | 3                 | 3                     |               |                                                                                 |  |  |  |

| PEM10,      | 2                 | 2                     | I, LVTTL      | Channel 1 Output Pre-emphasis Control Inputs                                    |  |  |  |

| PEM11       | 1                 | 1                     |               |                                                                                 |  |  |  |

| TDI         | 19                | 22                    | I, LVTTL      | Test Data Input to support IEEE 1149.1 features                                 |  |  |  |

| TDO         | 20                | 23                    | O, LVTTL      | Test Data Output to support IEEE 1149.1 features                                |  |  |  |

| TMS         | 18                | 21                    | I, LVTTL      | Test Mode Select to support IEEE 1149.1 features                                |  |  |  |

| TCK         | 17                | 19                    | I, LVTTL      | Test Clock to support IEEE 1149.1 features                                      |  |  |  |

| TRST        | 21                | 24                    | I, LVTTL      | Test Reset to support IEEE 1149.1 features                                      |  |  |  |

| N/C         | 8, 28             |                       |               | Not Connected                                                                   |  |  |  |

| POWER       |                   |                       |               |                                                                                 |  |  |  |

| $V_{DD}$    | 11, 14,           | 12, 16,               | I, Power      | $V_{DD}$ = 3.3V ±0.3V. At least 4 low ESR 0.01 µF bypass capacitors should be   |  |  |  |

|             | 16, 22,           | 18, 25,               |               | connected from V <sub>DD</sub> to GND plane.                                    |  |  |  |

|             | 25                | 29                    |               |                                                                                 |  |  |  |

| GND         | (Note 1)          | 5, 11, 15,            |               | Ground reference to LVDS and CMOS circuitry.                                    |  |  |  |

|             |                   | 20, 26,               |               | For the LLP package, the DAP is used as the primary GND connection to the       |  |  |  |

|             |                   | 30                    |               | device. The DAP is the exposed metal contact at the bottom of the LLP-28        |  |  |  |

|             |                   |                       |               | package. It should be connected to the ground plane with at least 4 vias for    |  |  |  |

|             |                   |                       |               | optimal AC and thermal performance.                                             |  |  |  |

Note 1: Note that for the LLP package GND is not an actual pin on the package, the GND is connected thru the DAP on the back side of the LLP package.

Note 2: The LVDS outputs do not support a multidrop (BLVDS) environment. The LVDS output characteristics of the SCAN90CP02 device have been optimized for point-to-point backplane and cable applications.

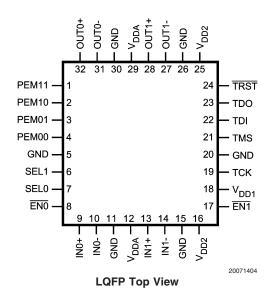

# **Connection Diagrams**

# **Configuration Select Truth Table**

| SEL0 | SEL1 | EN0 | EN1 | OUT0 | OUT1 | Mode                                              |

|------|------|-----|-----|------|------|---------------------------------------------------|

| 0    | 0    | 0   | 0   | IN0  | IN0  | 1:2 Splitter (IN1 powered down)                   |

| 0    | 1    | 0   | 0   | IN0  | IN1  | Dual Channel Repeater                             |

| 1    | 0    | 0   | 0   | IN1  | IN0  | Dual Channel Switch                               |

| 1    | 1    | 0   | 0   | IN1  | IN1  | 1:2 Splitter (IN0 powered down)                   |

| 0    | 1    | 0   | 1   | IN0  | PD   | Single Channel Repeater (Channel 1 powered down)  |

| 1    | 1    | 0   | 1   | IN1  | PD   | Single Channel Switch (IN0 and OUT1 powered down) |

| 0    | 0    | 1   | 0   | PD   | IN0  | Single Channel Switch (IN1 and OUT0 powered down) |

| 0    | 1    | 1   | 0   | PD   | IN1  | Single Channel Repeater (Channel 0 powered down)  |

| Х    | Х    | 1   | 1   | PD   | PD   | Both Channels in Power Down Mode                  |

| 0    | 0    | 0   | 1   |      |      | Invalid State*                                    |

| 1    | 0    | 0   | 1   |      |      | Invalid State*                                    |

| 1    | 0    | 1   | 0   |      |      | Invalid State*                                    |

| 1    | 1    | 1   | 0   |      |      | Invalid State*                                    |

PD = Power Down mode to minimize power consumption

# **Pre-emphasis**

The pre-emphasis is used to compensate for long or lossy transmission media. Separate pins are provided for each output to minimize power consumption. Pre-emphasis is programmable to be off or to preset values per the Pre-emphasis Control Selection Table.

# **Output Characteristics**

The output characteristics of the SCAN90CP02 device have been optimized for point-to-point backplane and cable applications.

#### **Pre-emphasis Control Selection Table**

| Chan        | nel 0 | Char  | nel 1 | Pre-emphasis |

|-------------|-------|-------|-------|--------------|

| PEM01 PEM00 |       | PEM11 | PEM10 |              |

| 0           | 0     | 0     | 0     | 0%           |

| 0           | 1     | 0     | 1     | 25%          |

| 1           | 0     | 1     | 0     | 50%          |

| 1           | 1     | 1     | 1     | 100%         |

X = Don't Care

<sup>\*</sup> Entering these states is not forbidden, however device operation is not defined in these states.

# **Applications Information**

FIGURE 2. SCAN90CP02 Configuration Select Decode

# **Absolute Maximum Ratings** (Note 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to +4.0VSupply Voltage (V<sub>DD</sub>) -0.3V to  $(V_{DD} + 0.3V)$ **CMOS Input Voltage** LVDS Receiver Input Voltage -0.3V to +3.6VLVDS Driver Output Voltage -0.3V to +3.6VLVDS Output Short Circuit Current 40mA Junction Temperature +150°C Storage Temperature -65°C to +150°C Lead Temperature +260°C

(Soldering, 4sec.)

Maximum Package Power Dissipation at 25°C

LLP-28 4.31 W LQFP-32 1.47W Derating above 25°C

LLP-28 34.5 mW/°C LQFP-32 11.8 mW/°C Thermal Resistance,  $\theta_{JA}$

LLP-28 29°C/W LQFP-32 85°C/W

ESD Rating

HBM, 1.5 kΩ, 100 pF 6.5 kV EIAJ, 0Ω, 200 pF >250V

# Recommended Operating Conditions

|                                        | Min | Тур | Max | Unit |  |

|----------------------------------------|-----|-----|-----|------|--|

| Supply Voltage (V <sub>DD</sub> - GND) | 3.0 | 3.3 | 3.6 | V    |  |

| Receiver Input Voltage                 | 0   |     | 3.6 | V    |  |

| Operating Free Air                     |     |     |     |      |  |

| Temperature                            | -40 | 25  | 85  | °C   |  |

| Junction Temperature                   |     |     | 150 | °C   |  |

## **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless other specified.

| Symbol                                                                                          | Parameter                                  | Conditions                                                        | Min                  | Typ<br>(Note 4) | Max      | Units |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|----------------------|-----------------|----------|-------|--|--|--|

| LVTTL DC SPECIFICATIONS (SEL0, SEL1, EN1, EN2, PEM00, PEM01, PEM10, PEM11, TDI, TCK, TMS, TRST) |                                            |                                                                   |                      |                 |          |       |  |  |  |

| V <sub>IH</sub>                                                                                 | High Level Input Voltage                   |                                                                   | 2.0                  |                 | $V_{DD}$ | V     |  |  |  |

| V <sub>IL</sub>                                                                                 | Low Level Input Voltage                    |                                                                   | GND                  |                 | 0.8      | V     |  |  |  |

| I <sub>IH</sub>                                                                                 | High Level Input Current                   | $V_{IN} = V_{DD} = V_{DDMAX}$                                     | -10                  |                 | +10      | μA    |  |  |  |

| I <sub>IL</sub>                                                                                 | Low Level Input Current                    | $V_{IN} = V_{SS}, V_{DD} = V_{DDMAX}$                             | -10                  |                 | +10      | μA    |  |  |  |

| I <sub>ILR</sub>                                                                                | Low Level Input Current                    | TDI, TMS, TRST                                                    | -40                  |                 | -200     | μA    |  |  |  |

| C <sub>IN1</sub>                                                                                | Input Capacitance                          | Any Digital Input Pin to V <sub>SS</sub>                          |                      | 3.5             |          | pF    |  |  |  |

| C <sub>OUT1</sub>                                                                               | Output Capacitance                         | Any Digital Output Pin to V <sub>SS</sub>                         |                      | 5.5             |          | pF    |  |  |  |

| V <sub>CL</sub>                                                                                 | Input Clamp Voltage                        | I <sub>CL</sub> = -18 mA                                          | -1.5                 | -0.8            |          | V     |  |  |  |

| V <sub>OH</sub>                                                                                 | High Level Output Voltage                  | $I_{OH} = -12 \text{ mA}, V_{DD} = 3.0 \text{ V}$                 | 2.4                  |                 |          | V     |  |  |  |

|                                                                                                 | (TDO)                                      | $I_{OH} = -100 \ \mu A, \ V_{DD} = 3.0 \ V$                       | V <sub>DD</sub> -0.2 |                 |          | V     |  |  |  |

| V <sub>OL</sub>                                                                                 | Low Level Output Voltage                   | $I_{OL} = 12 \text{ mA}, V_{DD} = 3.0 \text{ V}$                  |                      |                 | 0.5      | V     |  |  |  |

|                                                                                                 | (TDO)                                      | $I_{OL} = 100 \ \mu A, \ V_{DD} = 3.0 \ V$                        |                      |                 | 0.2      | V     |  |  |  |

| I <sub>os</sub>                                                                                 | Output Short Circuit Current               | TDO                                                               | -15                  |                 | -125     | mA    |  |  |  |

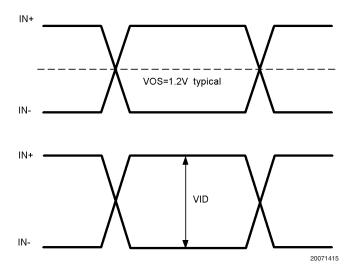

| LVDS INP                                                                                        | UT DC SPECIFICATIONS (IN0±, II             | N1±)                                                              |                      |                 |          |       |  |  |  |

| V <sub>TH</sub>                                                                                 | Differential Input High Threshold (Note 5) | $V_{CM} = 0.8V \text{ or } 1.2V \text{ or } 3.55V, V_{DD} = 3.6V$ |                      | 0               | 50       | mV    |  |  |  |

| V <sub>TL</sub>                                                                                 | Differential Input Low Threshold           | $V_{CM} = 0.8V \text{ or } 1.2V \text{ or } 3.55V, V_{DD} = 3.6V$ | -50                  | 0               |          | mV    |  |  |  |

| V <sub>ID</sub>                                                                                 | Differential Input Voltage                 | $V_{CM} = 0.8V$ to 3.55V, $V_{DD} = 3.6V$                         | 100                  |                 |          | mV    |  |  |  |

| V <sub>CMR</sub>                                                                                | Common Mode Voltage Range                  | $V_{ID} = 150 \text{ mV}, V_{DD} = 3.6 \text{V}$                  | 0.05                 |                 | 3.55     | V     |  |  |  |

| C <sub>IN2</sub>                                                                                | Input Capacitance                          | IN+ or IN- to V <sub>SS</sub>                                     |                      | 3.5             |          | pF    |  |  |  |

| I <sub>IN</sub>                                                                                 | Input Current                              | $V_{IN} = 3.6V$ , $V_{DD} = V_{DDMAX}$ or $0V$                    | -10                  |                 | +10      | μA    |  |  |  |

|                                                                                                 |                                            | $V_{IN} = 0V$ , $V_{DD} = V_{DDMAX}$ or $0V$                      | -10                  |                 | +10      | μA    |  |  |  |

**Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless other specified.

| Symbol                           | Parameter                                                | Conditions                                                                                                                  |         | Min  | Typ<br>(Note 4) | Max   | Units |

|----------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|------|-----------------|-------|-------|

| LVDS OU                          | TPUT DC SPECIFICATIONS (OUT                              | )±, OUT1±)                                                                                                                  |         |      |                 |       |       |

| V <sub>OD</sub>                  | Differential Output Voltage,<br>0% Pre-emphasis (Note 5) | 9 '   -                                                                                                                     |         | 250  | 400             | 575   | mV    |

| $\Delta V_{OD}$                  | Change in V <sub>OD</sub> between Complementary States   |                                                                                                                             |         | -35  |                 | 35    | mV    |

| Vos                              | Offset Voltage (Note 6)                                  |                                                                                                                             |         | 1.09 | 1.25            | 1.475 | V     |

| $\Delta V_{OS}$                  | Change in V <sub>OS</sub> between Complementary States   |                                                                                                                             |         | -35  |                 | 35    | mV    |

| I <sub>os</sub>                  | Output Short Circuit Current, One                        | OUT+ or OUT- Short to GND                                                                                                   |         |      | -15             | -40   | mA    |

|                                  | Complementary Output                                     | OUT+ or OUT- Short to V <sub>DD</sub>                                                                                       |         |      | 15              | 40    | mA    |

| I <sub>OSB</sub>                 | Output Short Circuit Current, both                       | OUT+ and OUT- Short to GND                                                                                                  |         |      | -15             | -30   | mA    |

|                                  | Complementary Outputs                                    | OUT+ and OUT- Short to V <sub>CM</sub>                                                                                      |         |      | 15              | 30    | mA    |

| $C_{OUT2}$                       | Output Capacitance                                       | OUT+ or OUT- to GND when TRI-STATE                                                                                          |         |      | 5.5             |       | pF    |

| SUPPLY                           | CURRENT (Static)                                         |                                                                                                                             |         |      |                 |       |       |

| I <sub>CC0</sub>                 | Supply Current                                           | All inputs and outputs enabled a active, terminated with differentia of 100Ω between OUT+ and OU                            | al load |      | 42              | 60    | mA    |

| I <sub>CC1</sub>                 | Supply Current - one channel powered down                | Single channel crossover switch<br>single channel repeater modes (<br>channel active, one channel in p<br>down mode)        |         | 22   | 30              | mA    |       |

| I <sub>CC2</sub>                 | Supply Current - one input powered down                  | Splitter mode (One input powere down, both outputs active)                                                                  | d       |      | 30              | 40    | mA    |

| I <sub>CCZ</sub>                 | TRI-STATE Supply Current                                 | Both input/output Channels in Po<br>Down Mode                                                                               | ower    |      | 1.4             | 2.5   | mA    |

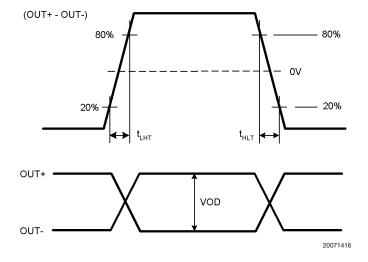

| SWITCHII                         | NG CHARACTERISTICS—LVDS O                                | UTPUTS (Figures 3, 4)                                                                                                       |         |      |                 |       |       |

| t <sub>LHT</sub>                 | Differential Low to High Transition<br>Time              | Use an alternating 1 and 0 pattern at 200 Mb/s, measure between 20% and                                                     |         | 70   | 150             | 215   | ps    |

| t <sub>HLT</sub>                 | Differential High to Low Transition Time                 | 80% of V <sub>OD</sub> .                                                                                                    |         | 50   | 135             | 180   | ps    |

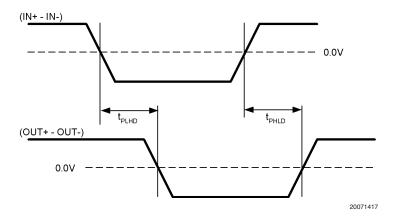

| t <sub>PLHD</sub>                | Differential Low to High<br>Propagation Delay            | Use an alternating 1 and 0 patte 200 Mb/s, measure at 50% V <sub>OD</sub>                                                   | rn at   | 0.5  | 2.4             | 3.5   | ns    |

| t <sub>PHLD</sub>                | Differential High to Low<br>Propagation Delay            | between input to output.                                                                                                    |         | 0.5  | 2.4             | 3.5   | ns    |

| t <sub>SKD1</sub>                | Pulse Skew                                               | It <sub>PLHD</sub> -t <sub>PHLD</sub>                                                                                       |         |      | 55              | 120   | ps    |

| t <sub>skcc</sub>                | Output Channel to Channel Skew                           | Difference in propagation delay ( or t <sub>PHLD</sub> ) among all output chanr Splitter mode (any one input to a outputs). | nels in | 0    | 130             | 315   | ps    |

| t <sub>JIT</sub> t <sub>ON</sub> | Jitter (0% Pre-emphasis)                                 | RJ - Alternating 1 and 0 at 750 M                                                                                           | ИНz     |      | 1.4             | 2.5   | psrms |

| 011                              | (Note 7)                                                 | DJ - K28.5 Pattern                                                                                                          | LQFP    |      | 110             | 140   | psp-p |

|                                  |                                                          | 1.5 Gbps                                                                                                                    | LLP     |      | 42              | 75    | psp-p |

|                                  |                                                          | TJ - PRBS 2 <sup>23</sup> -1 Pattern                                                                                        | LQFP    |      | 125             | 160   | psp-p |

|                                  |                                                          | 1.5 Gbps                                                                                                                    | LLP     |      | 105             | 140   | psp-p |

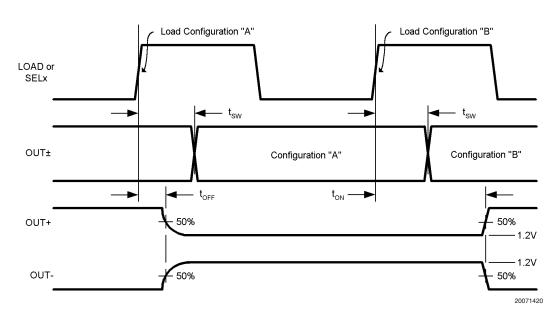

|                                  | LVDS Output Enable Time                                  | Time from ENx to OUT± change TRI-STATE to active.                                                                           | from    | 50   | 110             | 150   | ns    |

|                                  | LVDS Output Disable Time                                 | Time from ENx to OUT± change                                                                                                | from    |      | 5               | 12    |       |

#### **Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless other specified.

| Symbol          | Parameter           | Conditions                                | Min | Typ<br>(Note 4) | Max | Units |

|-----------------|---------------------|-------------------------------------------|-----|-----------------|-----|-------|

| t <sub>SW</sub> | LVDS Switching Time | Time from configuration select (SELx)     |     |                 |     |       |

|                 | SELx to OUT±        | to new switch configuration effective for |     | 110             | 150 | ns    |

|                 |                     | OUT±.                                     |     |                 |     |       |

#### **SCAN Circuitry Timing Requirements**

| Symbol           | Parameter                   | Conditions          | Min  | Тур | Max | Units |

|------------------|-----------------------------|---------------------|------|-----|-----|-------|

| f <sub>MAX</sub> | Maximum TCK Clock Frequency | $R_L = 500\Omega$ , | 25.0 |     |     | MHz   |

| t <sub>s</sub>   | TDI to TCK, H or L          | $C_L = 35 pF$       | 1.0  |     |     | ns    |

| t <sub>H</sub>   | TDI to TCK, H or L          |                     | 2.0  |     |     | ns    |

| t <sub>s</sub>   | TMS to TCK, H or L          |                     | 2.0  |     |     | ns    |

| t <sub>H</sub>   | TMS to TCK, H or L          |                     | 1.5  |     |     | ns    |

| t <sub>W</sub>   | TCK Pulse Width, H or L     |                     | 10.0 |     |     | ns    |

| t <sub>w</sub>   | TRST Pulse Width, L         |                     | 2.5  |     |     | ns    |

| t <sub>REC</sub> | Recovery Time, TRST to TCK  |                     | 2.0  |     |     | ns    |

Note 3: "Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

Note 4: Typical parameters are measured at V<sub>DD</sub> = 3.3V, T<sub>A</sub> = 25°C. They are for reference purposes, and are not production-tested.

Note 5: Differential output voltage V<sub>OD</sub> is defined as ABS(OUT+-OUT-). Differential input voltage V<sub>ID</sub> is defined as ABS(IN+-IN-).

Note 6: Output offset voltage  $V_{OS}$  is defined as the average of the LVDS single-ended output voltages at logic high and logic low states.

Note 7: JIT is the jitter from any input to any one differential LVDS output running at the specified data rate and data pattern, the other channel is powered off. Jitter is not production tested, but guaranteed through characterization on a sample basis. Random Jitter is measured RMS with a histogram including 1500 histogram window hits. K28.5 pattern is repeating bit streams of (0011111010 1100000101). This deterministic jitter or DJ pattern is measured to a histogram mean with a sample size of 350 hits. Total Jitter is measured peak to peak with a histogram including 3500 window hits.

# **Timing Diagrams**

FIGURE 3. LVDS Signals

# Timing Diagrams (Continued)

FIGURE 4. LVDS Output Transition Time

FIGURE 5. LVDS Output Propagation Delay

FIGURE 6. Configuration and Output Enable/Disable Timing

# **Typical Performance Characteristics for LLP Package**

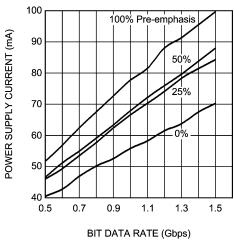

#### Power Supply Current vs. Bit Data Rate

2007144

Dynamic power supply current was measured while running a PRBS  $2^{23}$ -1 pattern in dual channel repeater mode.  $V_{CC}=3.3V$ ,  $T_{A}=+25^{\circ}C$ ,  $V_{ID}=0.5V$ ,  $V_{CM}=1.2V$

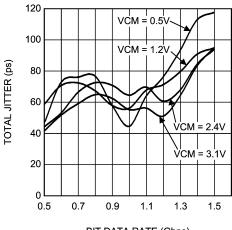

#### Total Jitter (T<sub>.1</sub>) vs. Bit Data Rate

BIT DATA RATE (Gbps)

20071442

Total Jitter measured at 0V differential while running a PRBS  $2^{23}$ -1 pattern in single channel repeater mode.  $V_{CC}=3.3V,\,T_A=+25^{\circ}C,\,V_{ID}=0.5V,\,0\%$  Pre-emphasis

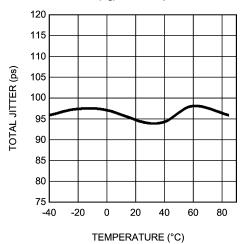

#### Total Jitter (T<sub>J</sub>) vs. Temperature

20071443

Dynamic power supply current was measured while running a PRBS 2 $^{23}$ -1 pattern in dual channel repeater mode. V<sub>CC</sub> = 3.3V, V<sub>ID</sub> = 0.5V, V<sub>CM</sub> = 1.2V, 1.5 Gbps data rate, 0% Pre-emphasis

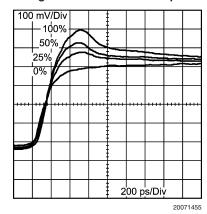

#### Positive Edge Transition vs. Pre-emphasis Level

FIGURE 7. Typical Performance Characteristics

## **Design-For-Test (DfT) Features**

#### **IEEE 1149.1 SUPPORT**

The SCAN90CP02 supports a fully compliant IEEE 1149.1 interface. The Test Access Port (TAP) provides access to boundary scan cells at each LVTTL I/O on the device for interconnect testing. The TAP also provides access to the IEEE 1149.6 test features if AC-coupled interconnects are used.

Refer to the BSDL file located on National's website for the details of the SCAN90CP02 IEEE 1149.1 implementation.

#### **IEEE 1149.6 SUPPORT**

AC-coupled differential interconnections on very high speed (1+ Gbps) data paths are not testable using traditional IEEE 1149.1 techniques. The IEEE 1149.1 structures and methods are intended to test static (DC-coupled), single ended networks. It is unable to test dynamic (AC-coupled) digital networks because the AC-coupling blocks static signals.

The SCAN90CP02 - which is intended for use in up to 1.5 Gbps data paths - has been designed with IEEE 1149.6 support to enable test of AC-coupled interconnects.

#### **FAULT INSERTION**

StuckAt is a feature that enables the user to override logic values on any of the external pins during normal operation. StuckAt can be thought of as having the same capabilities as the IEEE-1149.1 EXTEST instruction but on a per pin bases. Because this feature occurs on a per-pin basis, normal device operation (mission mode) is possible with the exception of the desired faults.

For more information on any of these features, refer to Application Note AN-1313, SCAN90CP02 Design-for-Test Features.

# Physical Dimensions inches (millimeters) unless otherwise noted DIMENSIONS ARE IN MILLIMETERS DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN (1) FOR REFERENCE ONLY RECOMMENDED LAND PATTERN PIN 1 INDEX AREA PIN 1 INDEX AREA AX 3 A

LLP, Plastic, QUAD,

Order Number SCAN90CP02SP (1000 piece Tape and Reel),

SCAN90CP02SPX (4500 piece Tape and Reel)

NS Package Number SPA28A

<u>nnaádna</u>

SPA28A (Rev A)

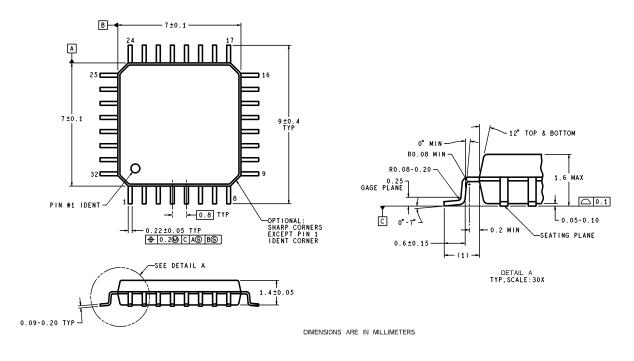

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

VBE32A (Rev E)

LQFP, Plastic, Quad

Order Number SCAN90CP02VY (250 piece Tray)

SCAN90CP02VYX (1000 piece Tape and Reel)

NS Package Number VBE32A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560