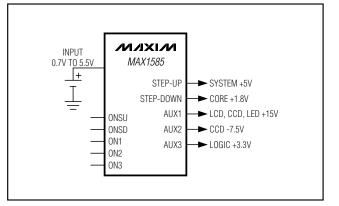

## **General Description**

The MAX1584/MAX1585 provide a complete powersupply solution for slim digital cameras. They improve performance, component count, and size compared to conventional multichannel controllers in 2-cell AA, 1-cell Li+, and dual-battery designs. On-chip MOSFETs provide up to 95% efficiency for critical power supplies, while additional channels operate with external FETs for optimum design flexibility. This optimizes overall efficiency and cost, while also reducing board space.

The MAX1584/MAX1585 include 5 high-efficiency DC-DC conversion channels:

- Step-up DC-DC converter with on-chip FETs

- Step-down DC-DC converter with on-chip FETs

- Three PWM DC-DC controllers for CCD, LCD, LED, or other functions

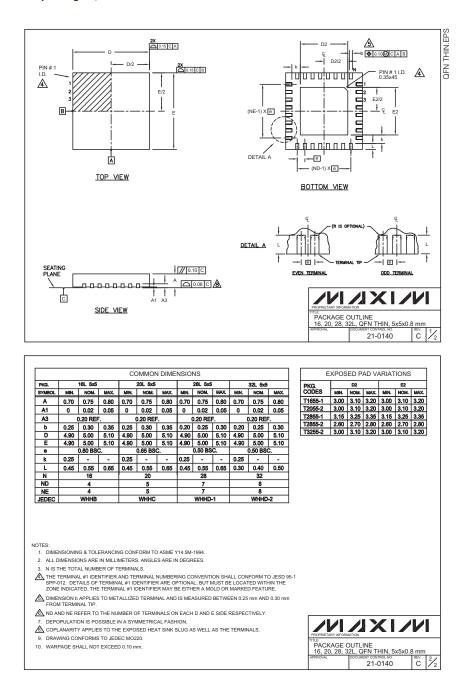

The step-down DC-DC converter can operate directly from the battery or from the step-up output, providing boost-buck capability with a compound efficiency of up to 90%. Both devices include three PWM DC-DC controllers: the MAX1584 includes two step-up controllers and one step-down controller, while the MAX1585 includes one step-up controller, one inverting controller, and one step-down controller. All DC-DC channels operate at one fixed frequency—settable from 100kHz to 1MHz—to optimize size, cost, and efficiency. Other features include soft-start, power-OK outputs, and overload protection. The MAX1584/MAX1585 are available in space-saving, 32-pin thin QFN packages. An evaluation kit is available to expedite designs.

Digital Cameras PDAs

**Applications**

##

\_Features

- Step-Up DC-DC Converter, 95% Efficient

- Step-Down DC-DC Converter Operate from Battery for 95% Efficient Step-Down 90% Efficient Boost-Buck with Step-Up

- Three Auxiliary PWM DC-DC Controllers

- No Transformers (MAX1585)

- Up to 1MHz Operating Frequency

- ImA Shutdown Mode

- Internal Soft-Start Control

- Overload Protection

- Compact 32-Pin Thin QFN Package (5mm x 5mm)

## **Ordering Information**

| PART       | TEMP RANGE     | PIN-<br>PACKAGE          | AUX<br>FUNCTIONS                        |

|------------|----------------|--------------------------|-----------------------------------------|

| MAX1584ETJ | -40°C to +85°C | 32 Thin QFN<br>5mm x 5mm | 2 step-up<br>1 step-down                |

| MAX1585ETJ | -40°C to +85°C | 32 Thin QFN<br>5mm x 5mm | 1 step-up<br>1 step-down<br>1 inverting |

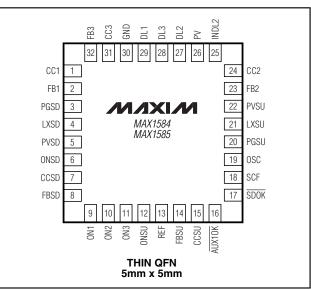

## Pin Configuration

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| PV, PVSU, PVSD, SDOK, AUX10K, |                        |

|-------------------------------|------------------------|

| GND                           | 0.3V to +6V            |

| PGND to GND                   | 0.3V to +0.3V          |

| INDL2, DL1, DL3 to GND        | 0.3V to (PVSU + 0.3V)  |

| DL2 to GND                    | 0.3V to (INDL2 + 0.3V) |

| PV to PVSU                    | -0.3V to + 0.3V        |

| LXSU Current (Note 1)         |                        |

| LXSD Current (Note 1)         | 2.25A                  |

| REF, OSC, CC to GND           |                        |

Continuous Power Dissipation (T<sub>A</sub> = +70°C) 32-Pin Thin QFN (derate 22mW/°C above +70°C) ....1700mW Operating Temperature Range .....-40°C to +85°C Junction Temperature ......+150°C Storage Temperature Range .....-65°C to +150°C Lead Temperature (soldering, 10s) .....+300°C

Note 1: LXSU has internal clamp diodes to PVSU and PGND, and LXSD has internal clamp diodes to PVSD and PGND. Applications that forward bias these diodes should take care not to exceed the device's power dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(VPVSU = VPV = VPVSD = VINDL2 = 3.6V, TA = 0°C to +85°C, unless otherwise noted.)

| PARAMETER                                                                    | CONDITIONS                                                                                         | MIN   | ТҮР  | MAX   | UNITS |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| GENERAL                                                                      |                                                                                                    |       |      |       |       |

| Input Voltage Range                                                          | (Note 2)                                                                                           | 0.7   |      | 5.5   | V     |

| Step-Up Minimum Startup<br>Voltage                                           | $I_{LOAD} < 1$ mA, T <sub>A</sub> = +25°C, startup voltage tempco is<br>-2300ppm/°C (typ) (Note 3) |       | 0.9  | 1.1   | V     |

| Shutdown Supply Current into PV                                              | PV = 3.6V                                                                                          |       | 0.1  | 5     | μΑ    |

| Supply Current into PV with<br>Step-Up Enabled                               | ONSU = 3.6V, FBSU = 1.5V<br>(does not include switching losses)                                    |       | 300  | 450   | μA    |

| Supply Current into PV with<br>Step-Up and Step-Down Enabled                 | ONSU = ONSD = 3.6V, FBSU = 1.5V, FBSD = 1.5V<br>(does not include switching losses)                |       | 450  | 700   | μA    |

| Total Supply Current from PV and<br>PVSU with Step-Up and One AUX<br>Enabled | ONSU = ON1 = 3.6V, FBSU = 1.5V, FB2 = 1.5V<br>(does not include switching losses)                  |       | 400  | 650   | μA    |

| REFERENCE                                                                    |                                                                                                    |       |      |       |       |

| Reference Output Voltage                                                     | $I_{\text{REF}} = 20\mu\text{A}$                                                                   | 1.23  | 1.25 | 1.27  | V     |

| Reference Load Regulation                                                    | 10μΑ < I <sub>REF</sub> < 200μΑ                                                                    |       | 4.5  | 10    | mV    |

| Reference Line Regulation                                                    | 2.7 < PVSU < 5.5V                                                                                  |       | 1.3  | 5     | mV    |

| OSCILLATOR                                                                   |                                                                                                    |       |      |       |       |

| OSC Discharge Trip Level                                                     | Rising edge                                                                                        | 1.225 | 1.25 | 1.275 | V     |

| OSC Discharge Resistance                                                     | $OSC = 1.5V, I_{OSC} = 3mA$                                                                        |       | 52   | 80    | Ω     |

| OSC Discharge Pulse Width                                                    |                                                                                                    |       | 150  |       | ns    |

| OSC Frequency                                                                | $R_{OSC} = 47 k\Omega$ , $C_{OSC} = 100 pF$                                                        |       | 500  |       | kHz   |

| STEP-UP DC-DC CONVERTER                                                      |                                                                                                    |       |      |       |       |

| Step-Up Startup-to-Normal<br>Operating Threshold                             | Rising edge or falling edge (Note 4)                                                               | 2.30  | 2.5  | 2.65  | V     |

| Step-Up Startup-to-Normal<br>Operating Threshold Hysteresis                  |                                                                                                    |       | 80   |       | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PVSU} = V_{PV} = V_{PVSD} = V_{INDL2} = 3.6V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted.)

| PARAMETER                                                 | CONDITIONS                                 | MIN   | ТҮР   | MAX   | UNITS         |

|-----------------------------------------------------------|--------------------------------------------|-------|-------|-------|---------------|

| Step-Up Voltage Adjust Range                              |                                            | 3.0   |       | 5.5   | V             |

| Start Delay of ONSD, ON1, ON2, ON3 after SU in Regulation |                                            |       | 1024  |       | OSC<br>cycles |

| FBSU Regulation Voltage                                   |                                            | 1.231 | 1.25  | 1.269 | V             |

| FBSU to CCSU<br>Transconductance                          | FBSU = CCSU                                | 80    | 135   | 185   | μS            |

| FBSU Input Leakage Current                                | FBSU = 1.25V                               | -100  | +1    | +100  | nA            |

| Idle Mode <sup>™</sup> Trip Level                         | (Note 6)                                   |       | 150   |       | mA            |

| Current-Sense Amplifier<br>Transresistance                |                                            |       | 0.275 |       | V/A           |

| Step-Up Maximum Duty Cycle                                | FBSU = 1V                                  | 80    | 85    | 90    | %             |

| PVSU Leakage Current                                      | $V_{LX} = 0V, PVSU = 5.5V$                 |       | 0.1   | 5     | μA            |

| LXSU Leakage Current                                      | $V_{LXSU} = V_{OUT} = 5.5V$                |       | 0.1   | 5     | μΑ            |

| Switch On-Resistance                                      | N channel                                  |       | 95    | 150   | m0            |

| Switch On-Resistance                                      | P channel                                  |       | 150   | 250   | mΩ            |

| N-Channel Current Limit                                   |                                            | 2.4   | 2.8   | 3.2   | А             |

| P-Channel Turn-Off Current                                |                                            |       | 20    |       | mA            |

| Startup Current Limit                                     | PVSU = 1.8V (Note 5)                       |       | 450   |       | mA            |

| Startup tOFF                                              | PVSU = 1.8V                                |       | 700   |       | ns            |

| Startup Frequency                                         | PVSU = 1.8V                                |       | 200   |       | kHz           |

| STEP-DOWN DC-DC CONVERT                                   | ER                                         |       |       |       |               |

| Step-Down Output Voltage<br>Adjust Range                  | PVSD must be greater than output (Note 7)  | 1.25  |       | 5.00  | V             |

| FBSD Regulation Voltage                                   |                                            | 1.231 | 1.25  | 1.269 | V             |

| FBSD to CCSD<br>Transconductance                          | FBSD = CCSD                                | 80    | 135   | 185   | μS            |

| FBSD Input Leakage Current                                | FBSD = 1.25V                               | -100  | +0.1  | +100  | nA            |

| Idle Mode Trip Level                                      | (Note 6)                                   |       | 100   |       | mA            |

| Current-Sense Amplifier<br>Transresistance                |                                            |       | 0.5   |       | V/A           |

| LXSD Leakage Current                                      | V <sub>LXSD</sub> = 0 to 3.6V, PVSU = 3.6V |       | 0.1   | 5     | μA            |

| Quitate On David                                          | N channel                                  |       | 95    | 150   |               |

| Switch On-Resistance                                      | P channel                                  |       | 150   | 250   | mΩ            |

| P-Channel Current Limit                                   |                                            | 0.65  | 0.8   | 0.95  | А             |

| N-Channel Turn-Off Current                                |                                            |       | 20    |       | mA            |

| Soft-Start Interval                                       |                                            |       | 2048  |       | OSC<br>cycles |

| SDOK Output Low Voltage                                   | 0.1mA into SDOK                            |       | 0.01  | 0.1   | V             |

| SDOK Leakage Current                                      | ONSU = GND                                 |       | 0.01  | 1     | μA            |

Idle Mode is a trademark of Maxim Integrated Products, Inc.

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PVSU} = V_{PV} = V_{PVSD} = V_{INDL2} = 3.6V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted.)

| PARAMETER                                      | CONDITIONS                     | MIN                        | ТҮР     | MAX   | UNITS         |

|------------------------------------------------|--------------------------------|----------------------------|---------|-------|---------------|

| AUX1, 2, 3 DC-DC CONTROLLE                     | RS                             | •                          |         |       |               |

| Maximum Duty Cycle                             | FB_ = 1V                       | 80                         | 85      | 90    | %             |

| FB1 and FB3 Regulation Voltage                 | $FB_ = CC_$                    | 1.231                      | 1.25    | 1.269 | V             |

| FB2 (MAX1584) Regulation<br>Voltage            | FB_ = CC_                      | 1.231                      | 1.25    | 1.269 | V             |

| FB2 (MAX1585) (Inverter)<br>Regulation Voltage | FB_ = CC_                      | -0.01                      | 0       | +0.01 | V             |

| FB_ to CC_ Transconductance                    | FB_ = CC_                      | 80                         | 135     | 185   | μS            |

| FB_ Input Leakage Current                      | FB_ = 1.25V                    | -100                       | +1      | +100  | nA            |

| DL_ Driver Resistance                          | Output high or low             |                            | 2.5     | 10    | Ω             |

| DL_ Drive Current                              | Sourcing or sinking            |                            | 0.5     |       | А             |

| Soft-Start Interval                            |                                |                            | 4096    |       | OSC<br>cycles |

| AUX10K Output Low Voltage                      | 0.1mA into AUX10K              |                            | 0.01    | 0.1   | V             |

| AUX10K Leakage Current                         | ONSU = GND                     |                            | 0.01    | 1     | μΑ            |

| OVERLOAD AND THERMAL PR                        | OTECTION                       |                            |         |       | 1             |

| Overload-Protection Fault Delay                |                                |                            | 100,000 |       | OSC<br>cycles |

| SCF Leakage Current                            | ONSU = PVSU, FBSU = 1.5V       |                            | 0.1     | 1     | μΑ            |

| SCF Output Low Voltage                         | 0.1mA into SCF                 |                            | 0.01    | 0.1   | V             |

| Thermal Shutdown                               |                                |                            | +160    |       | °C            |

| Thermal Hysteresis                             |                                |                            | 20      |       | °C            |

| LOGIC INPUTS                                   |                                |                            |         |       |               |

| ON_ Input Low Level                            | 1.1V < PVSU < 1.8V (ONSU only) |                            |         | 0.2   | v             |

|                                                | 1.8V < PVSU< 5.5V              |                            |         | 0.4   | v             |

| ON_ Input High Level                           | 1.1V < PVSU < 1.8V (ONSU only) | V <sub>PVSU</sub> -<br>0.2 |         |       | V             |

|                                                | 1.8V < PVSU < 5.5V             | 1.6                        |         |       |               |

| ON_ Impedance to GND                           | ON_ = 3.35V                    |                            | 330     |       | kΩ            |

## **ELECTRICAL CHARACTERISTICS**

$(V_{PVSU} = V_{PV} = V_{PVSD} = V_{INDL2} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 8)

| PARAMETER                                                                    | CONDITIONS                                                                          | MIN   | MAX   | UNITS |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|

| GENERAL                                                                      | •                                                                                   | •     |       | •     |

| Input Voltage Range                                                          | (Note 2)                                                                            | 0.7   | 5.5   | V     |

| Shutdown Supply Current into PVSU                                            | PVSU = 3.6V                                                                         |       | 5     | μA    |

| Supply Current into PV with<br>Step-Up Enabled                               | ONSU = 3.6V, FBSU = 1.5V<br>(does not include switching losses)                     |       | 450   | μΑ    |

| Supply Current into PV with<br>Step-Up and Step-Down Enabled                 | ONSU = ONSD = 3.6V, FBSU = 1.5V, FBSD = 1.5V<br>(does not include switching losses) |       | 700   | μΑ    |

| Total Supply Current from PV and<br>PVSU with Step-Up and One AUX<br>Enabled | ONSU = ON1 = 3.6V, FBSU = 1.5V, FB2 = 1.5V<br>(does not include switching losses)   |       | 650   | μΑ    |

| REFERENCE                                                                    |                                                                                     |       |       |       |

| Reference Output Voltage                                                     | $I_{\text{REF}} = 20 \mu A$                                                         | 1.225 | 1.275 | V     |

| Reference Load Regulation                                                    | 10μΑ < I <sub>REF</sub> < 200μΑ                                                     |       | 10    | mV    |

| Reference Line Regulation                                                    | 2.7V < PVSU < 5.5V                                                                  |       | 5     | mV    |

| OSCILLATOR                                                                   |                                                                                     |       |       |       |

| OSC Discharge Trip Level                                                     | Rising edge                                                                         | 1.225 | 1.275 | V     |

| OSC Discharge Resistance                                                     | $OSC = 1.5V, I_{OSC} = 3mA$                                                         |       | 80    | Ω     |

| STEP-UP DC-DC CONVERTER                                                      |                                                                                     |       |       |       |

| Step-Up Startup-to-Normal<br>Operating Threshold                             | Rising edge or falling edge (Note 4)                                                | 2.30  | 2.65  | V     |

| Step-Up Voltage Adjust Range                                                 |                                                                                     | 3.0   | 5.5   | V     |

| FBSU Regulation Voltage                                                      |                                                                                     | 1.225 | 1.275 | V     |

| FBSU to CCSU<br>Transconductance                                             | FBSU = CCSU                                                                         | 80    | 185   | μS    |

| FBSU Input Leakage Current                                                   | FBSU = 1.25V                                                                        | -100  | +100  | nA    |

| Step-Up Maximum Duty Cycle                                                   | FBSU = 1V                                                                           | 80    | 90    | %     |

| PVSU Leakage Current                                                         | $V_{LX} = 0V, PVSU = 5.5V$                                                          |       | 5     | μA    |

| LXSU Leakage Current                                                         | $V_{LXSU} = V_{OUT} = 5.5V$                                                         |       | 5     | μA    |

| Quitab On Desistance                                                         | N channel                                                                           |       | 150   |       |

| Switch On-Resistance                                                         | P channel                                                                           |       | 250   | mΩ    |

| N-Channel Current Limit                                                      |                                                                                     | 2.4   | 3.2   | А     |

| STEP-DOWN DC-DC CONVERTE                                                     | R                                                                                   |       |       |       |

| Step-Down Output Voltage Adjust<br>Range                                     | PVSD must be greater than output (Note 7)                                           | 1.25  | 5.00  | V     |

## ELECTRICAL CHARACTERISTICS (continued)

$(V_{PVSU} = V_{PV} = V_{PVSD} = V_{INDL2} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 8)

| PARAMETER                                      | CONDITIONS                                 | MIN                     | MAX   | UNITS |  |

|------------------------------------------------|--------------------------------------------|-------------------------|-------|-------|--|

| FBSD Regulation Voltage                        |                                            | 1.225                   | 1.275 | V     |  |

| FBSD to CCSD<br>Transconductance               | FBSD = CCSD                                | 80                      | 185   | μS    |  |

| FBSD Input Leakage Current                     | FBSD = 1.25V                               | -100                    | +100  | nA    |  |

| LXSD Leakage Current                           | V <sub>LXSD</sub> = 0 to 3.6V, PVSU = 3.6V |                         | 5     | μΑ    |  |

| Switch On-Resistance                           | N channel                                  |                         | 150   | mΩ    |  |

| Switch On-nesistance                           | P channel                                  |                         | 250   | 11152 |  |

| P-Channel Current Limit                        |                                            | 0.65                    | 0.95  | А     |  |

| SDOK Output Low Voltage                        | 0.1mA into SDOK                            |                         | 0.1   | V     |  |

| SDOK Leakage Current                           | ONSU = GND                                 |                         | 1     | μA    |  |

| AUX1, 2, 3 DC-DC CONTROLLER                    | RS                                         |                         |       |       |  |

| Maximum Duty Cycle                             | $FB_{=} = 1V$                              | 80                      | 90    | %     |  |

| FB1 and FB3 Regulation Voltage                 | $FB_ = CC_$                                | 1.225                   | 1.275 | V     |  |

| FB2 (MAX1584) Regulation<br>Voltage            | FB_ = CC_                                  | 1.225                   | 1.275 | V     |  |

| FB2 (MAX1585) (Inverter)<br>Regulation Voltage | FB_ = CC_                                  | -0.01                   | +0.01 | V     |  |

| FB_ to CC_ Transconductance                    | FB_ = CC_                                  | 80                      | 185   | μS    |  |

| FB_ Input Leakage Current                      | FB_ = 1.25V                                | -100                    | +100  | nA    |  |

| DL_ Driver Resistance                          | Output high or low                         |                         | 10    | Ω     |  |

| AUX10K Output Low Voltage                      | 0.1mA into AUX10K                          |                         | 0.1   | V     |  |

| AUX10K Leakage Current                         | ONSU = GND                                 |                         | 1     | μΑ    |  |

| OVERLOAD AND THERMAL PRO                       | DTECTION                                   | ·                       |       |       |  |

| SCF Leakage Current                            | ONSU = PVSU, FBSU = 1.5V                   |                         | 1     | μΑ    |  |

| SCF Output Low Voltage                         | 0.1mA into SCF                             |                         | 0.1   | V     |  |

| LOGIC INPUTS                                   |                                            | ·                       |       |       |  |

|                                                | 1.1V < PVSU < 1.8V (ONSU only)             |                         | 0.2   | V     |  |

| ON_ Input Low Level                            | 1.8V < PVSU < 5.5V                         |                         | 0.4   | v     |  |

|                                                | 1.1V < PVSU < 1.8V (ONSU only)             | V <sub>PVSU</sub> - 0.2 |       | V     |  |

| ON_ Input High Level                           | 1.8V < PVSU < 5.5V                         | 1.6                     |       | ר ∨   |  |

Note 2: The MAX1584/MAX1585 are powered from the step-up output (PVSU). An internal low-voltage startup oscillator drives the step-up starting at about 0.9V until PVSU reaches approximately 2.5V. When PVSU reaches 2.5V, the main control circuitry takes over. Once the step-up is up and running, it can maintain operation with very low input voltages; however, output current is limited.

**Note 3:** Since the device is powered from PVSU, a Schottky rectifier, connected from the input battery to PVSU, is required for low-voltage startup, or if PVSD is connected to V<sub>IN</sub> instead of PVSU.

Note 4: The step-up regulator is in startup mode until this voltage is reached. Do not apply full load current during startup. A power-OK output can be used with an external PFET to gate the load until the step-up is in regulation. See the *Applications Information* section.

M/XI/M

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>PVSU</sub> = V<sub>PV</sub> = V<sub>PVSD</sub> = V<sub>INDL2</sub> = 3.6V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 8)

Note 5: The step-up current limit in startup refers to the LXSU switch current limit, not an output current limit.

- **Note 6:** The idle mode current threshold is the transition point between fixed-frequency PWM operation and idle mode operation (where switching rate varies with load). The specification is given in terms of inductor current. In terms of output current, the idle mode transition varies with input-output voltage ratio and inductor value. For the step-up, the transition output current is approximately 1/3 the inductor current when stepping from 2V to 3.3V. For the step-down, the transition current in terms of output current is approximately 3/4 the inductor current when stepping down from 3.3V to 1.8V.

- Note 7: Operation in dropout (100% duty cycle) can only be maintained for 100,000 OSC cycles before the output is considered faulted, triggering global shutdown.

- Note 8: Specifications to -40°C are guaranteed by design, not production tested.

8

MAX1584/MAX1585

## \_\_\_\_\_Pin Description

| -   |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | CC1  | AUX1 Controller Compensation Node. Connect a series resistor-capacitor from CC1 to GND to compensate the converter control loop. This pin is actively driven to GND in shutdown, overload, and thermal limit. See the <i>AUX Compensation</i> section.                                                                                                                                                                                                          |

| 2   | FB1  | AUX1 Controller Feedback Input. The feedback threshold is 1.25V. This pin is high impedance in shutdown.                                                                                                                                                                                                                                                                                                                                                        |

| 3   | PGSD | Step-Down Power Ground. Connect all PG_ pins together and to GND with short traces as close as possible to the IC.                                                                                                                                                                                                                                                                                                                                              |

| 4   | LXSD | Step-Down Converter Switching Node. Connect to the inductor of the step-down converter. LXSD is high impedance in shutdown.                                                                                                                                                                                                                                                                                                                                     |

| 5   | PVSD | Step-Down Converter Input. PVSD can connect to PVSU, effectively making OUTSD a boost-buck output from the battery. Bypass to GND with a 1 $\mu$ F ceramic capacitor if connected to PVSU. PVSD can also be connected to the battery but should not exceed PVSU by more than a Schottky diode forward voltage. Bypass PVSD with a 10 $\mu$ F ceramic capacitor when connecting to the battery input. A 10k $\Omega$ internal resistance connects PVSU and PVSD. |

| 6   | ONSD | Step-Down Converter On/Off Control Input. Logic high = on; however, turn-on is locked out until the step-<br>up has reached regulation. This pin has an internal $330k\Omega$ pulldown resistance to GND.                                                                                                                                                                                                                                                       |

| 7   | CCSD | Step-Up Converter Compensation Node. Connect a series resistor-capacitor from CCSD to GND to compensate the converter control loop. This pin is actively driven to GND in shutdown, overload, and thermal limit. See the <i>Step-Down Compensation</i> section.                                                                                                                                                                                                 |

| 8   | FBSD | Step-Down Converter Feedback Input. Connect a resistive voltage-divider from OUTSD to FBSD to GND. The FBSD feedback threshold is 1.25V. This pin is high impedance in shutdown.                                                                                                                                                                                                                                                                                |

| 9   | ON1  | AUX1 Controller On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the step-up has reached regulation. This pin has an internal $330k\Omega$ pulldown resistance to GND.                                                                                                                                                                                                                                                 |

| 10  | ON2  | AUX2 Controller On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the step-up has reached regulation. This pin has an internal $330k\Omega$ pulldown resistance to GND.                                                                                                                                                                                                                                                 |

| 11  | ON3  | AUX3 Controller On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the step-up has reached regulation. This pin has an internal $330k\Omega$ pulldown resistance to GND.                                                                                                                                                                                                                                                 |

| 12  | ONSU | Step-Up Converter On/Off Control. Logic high = on. All other ON_ pins are locked out until 1024 OSC cycles after the step-up DC-DC converter output has reached its final value. This pin has an internal $330k\Omega$ pulldown resistance to GND.                                                                                                                                                                                                              |

| 13  | REF  | Reference Output. Bypass REF to GND with a $0.1\mu$ F or greater capacitor. The maximum allowed load on REF is 200 $\mu$ A. REF is actively pulled to GND when all converters are shut down.                                                                                                                                                                                                                                                                    |

| 14  | FBSU | Step-Up Converter Feedback Input. Connect a resistive voltage-divider from PVSU to FBSU to GND. The FBSU feedback threshold is 1.25V. This pin is high impedance in shutdown.                                                                                                                                                                                                                                                                                   |

| 15  | CCSU | Step-Up Converter Compensation Node. Connect a series resistor-capacitor from CCSU to GND to compensate the converter control loop. This pin is actively driven to GND in shutdown, overload, and thermal limit. See the <i>Step-Up Compensation</i> section.                                                                                                                                                                                                   |

## Pin Description (continued)

| PIN | NAME                                                                          |                                                                                                                                                                                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-----|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 16  | AUX10K                                                                        |                                                                                                                                                                                | UX1 Controller. AUX1OK is low when the AUX1 controller has This pin is high impedance in shutdown, overload, and thermal limit.                                                                                                                                                                                                                                         |  |  |  |  |

| 17  | SDOK                                                                          |                                                                                                                                                                                | tep-Down Converter. SDOK is low when the step-down has successfully gh impedance in shutdown, overload, and thermal limit.                                                                                                                                                                                                                                              |  |  |  |  |

| 18  | SCF                                                                           | occurs and during startup. SCF ca<br>completely disconnect the load wh                                                                                                         | hort-Circuit Flag, Active-Low, Open-Drain Output. SCF is high impedance when overload protection ccurs and during startup. SCF can drive high-side PFET switches connected to one or more outputs to completely disconnect the load when the channel turns off in response to a logic command or an verload. See the <i>Status Outputs (SDOK, AUX10K, SCF)</i> section. |  |  |  |  |

| 19  | OSC                                                                           | (or other DC voltage) to set the ose                                                                                                                                           | g capacitor from OSC to GND and a timing resistor from OSC to PVSU cillator frequency between 100kHz and 1MHz. See the <i>Setting the</i> pin is high impedance in shutdown.                                                                                                                                                                                            |  |  |  |  |

| 20  | PGSU                                                                          | Step-Up Power Ground. Connect a possible.                                                                                                                                      | all PG_ pins together and to GND with short traces as close to the IC as                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 21  | LXSU                                                                          | Step-Up Converter Switching Node impedance in shutdown.                                                                                                                        | e. Connect to the inductor of the step-up converter. LXSU is high                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 22  | PVSU                                                                          |                                                                                                                                                                                | DC Converter. Connect the output filter capacitor from PVSU to PGSU.<br>rter channels. Connect PVSU to PV at the IC.                                                                                                                                                                                                                                                    |  |  |  |  |

|     | AUX2 Controller Feedback Input.<br>This pin is high impedance in<br>shutdown. |                                                                                                                                                                                | <b>MAX1585 (AUX2 inverter):</b> The FB2 feedback threshold is 0V.<br>Connect a resistive voltage-divider from the output voltage to FB2 to<br>REF to set the output voltage.                                                                                                                                                                                            |  |  |  |  |

| 23  |                                                                               | <b>MAX1584 (AUX2 step-up):</b> The FB2 feedback threshold is 1.25V.<br>Connect a resistive voltage-divider from the output voltage to FB2 to<br>GND to set the output voltage. |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 24  | CC2                                                                           |                                                                                                                                                                                | ode. Connect a series resistor-capacitor from CC2 to GND to is actively driven to GND in shutdown and thermal limit. See the AUX                                                                                                                                                                                                                                        |  |  |  |  |

| 25  | INDL2                                                                         | Voltage Input for the AUX2 Gate<br>Driver. The voltage at INDL2 sets                                                                                                           | <b>MAX1585 (AUX2 inverter):</b> Connect INDL2 to the external P channel MOSFET source (typically the battery) to ensure the P channel is completely off when D2 swings high.                                                                                                                                                                                            |  |  |  |  |

|     | the high gate-drive voltage.                                                  | MAX1584 (AUX2 step-up): Connect INDL2 to PVSU for optimum N-channel gate drive.                                                                                                |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 26  | PV                                                                            | IC Power Input. Connect PVSU and                                                                                                                                               | d PV together.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     |                                                                               | AUX2 Controller Gate-Drive                                                                                                                                                     | <b>MAX1585:</b> DL2 drives a PFET in an inverter configuration. In shutdown, overload, and thermal limit, DL2 is driven high.                                                                                                                                                                                                                                           |  |  |  |  |

| 27  | DL2                                                                           | Output. DL2 drives between<br>INDL2 and GND.                                                                                                                                   | <b>MAX1584:</b> DL2 drives an N-channel FET in a boost/flyback configuration. In shutdown, overload, and thermal limit, DL2 is driven low.                                                                                                                                                                                                                              |  |  |  |  |

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                 |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | DL3  | AUX3 Step-Down Controller Gate-Drive Output. Connect to the gate of a P-channel MOSFET. DL3 swings from GND to PVSU and supplies up to 500mA. DL3 is driven to PVSU in shutdown and thermal limit.                                                                                                                                                       |

| 29  | DL1  | AUX1 Step-Up Controller Gate-Drive Output. Connect to the gate of an N-channel MOSFET. DL1 swings from GND to PVSU and supplies up to 500mA. DL1 is driven to GND in shutdown and thermal limit.                                                                                                                                                         |

| 30  | GND  | Analog Ground. Connect to all PG_ pins as close to the IC as possible.                                                                                                                                                                                                                                                                                   |

| 31  | CC3  | AUX3 Step-Down Controller Compensation Node. Connect a series resistor-capacitor from CC3 to FB3 to compensate the converter control loop. This pin is actively driven to GND in shutdown, overload, and thermal limit. See the <i>AUX Compensation</i> section.                                                                                         |

| 32  | FB3  | PWM Step-Up Controller 3 Feedback Input. Connect a resistive voltage-divider from the output voltage to FB3 to GND to set the output voltage. The FB3 feedback threshold is 1.25V. This pin is high impedance in shutdown.                                                                                                                               |

| PAD | EP   | Exposed Underside Metal Pad. This pad must be soldered to the PC board to achieve package thermal and mechanical ratings. There is no internal metal or bond wire physically connecting the exposed pad to the GND pin(s). Connecting the exposed pad to ground does not remove the requirement for a good ground connection to the appropriate IC pins. |

## **Detailed Description**

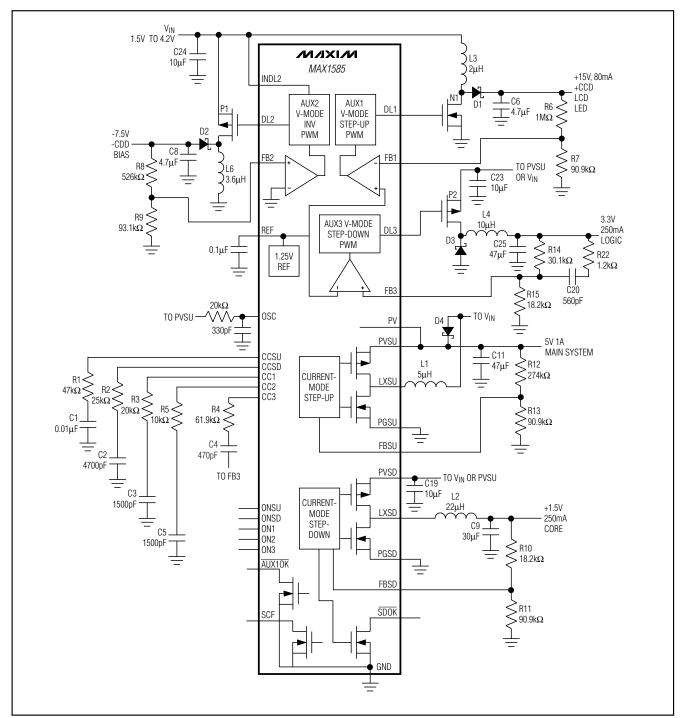

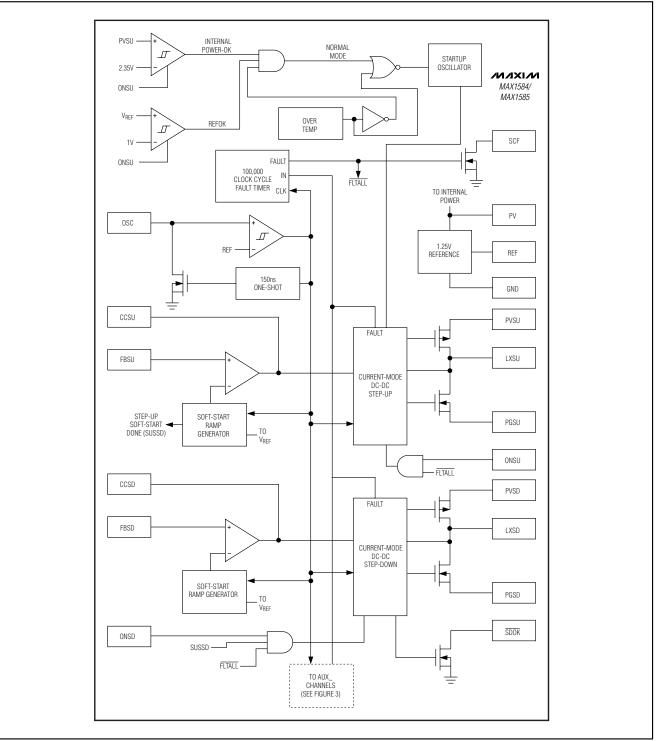

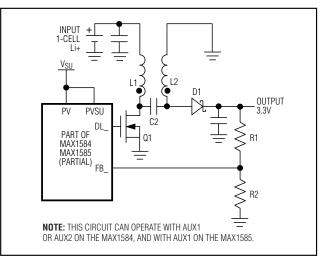

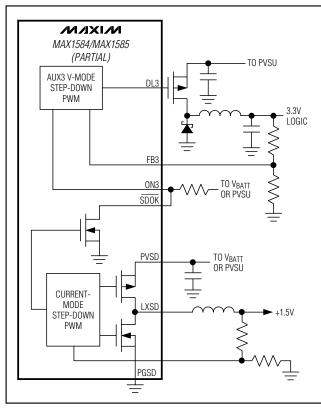

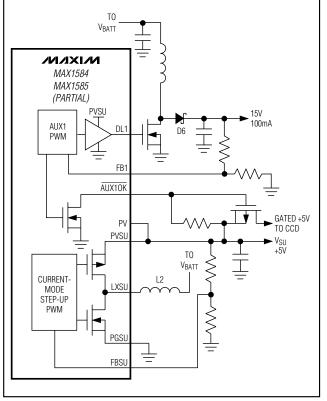

The MAX1584/MAX1585 are complete power-conversion ICs for slim digital still cameras. They can accept input from a variety of sources, including single-cell Li+ batteries and 2-cell alkaline or NiMH batteries, as well as systems designed to accept both battery types. The MAX1584/MAX1585 include five DC-DC converter channels to generate all required voltages (Figure 2 shows a functional diagram):

- Synchronous-rectified step-up DC-DC converter with on-chip MOSFETs—Typically supplies 3.3V for main system power or 5V to power other DC-DC converters for boost-buck designs.

- Synchronous-rectified step-down DC-DC converter with on-chip MOSFETs—Typically supplies 1.8V for the DSP core. Powering the step-down from the step-up output provides efficient (up to 90%) boostbuck functionality that supplies a regulated output when the battery voltage is above or below the output voltage. The step-down can also be powered from the battery if there is sufficient headroom.

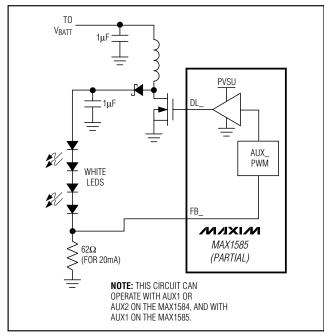

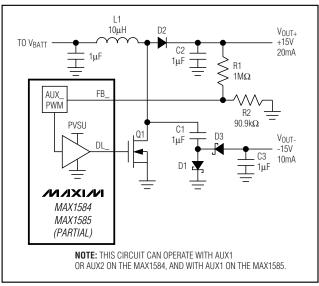

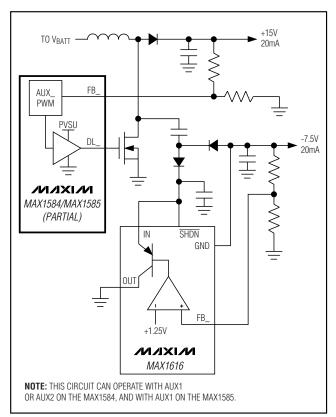

- AUX1 step-up controller—Typically used for 15V to bias one or more of the LCD, CCD, and LED backlights.

- AUX2 step-up controller (MAX1584)—Typically supplies remaining bias voltages with either a multi-output flyback transformer or a boost converter with charge-pump inverter. Alternately, can power white LEDs for LCD backlighting.

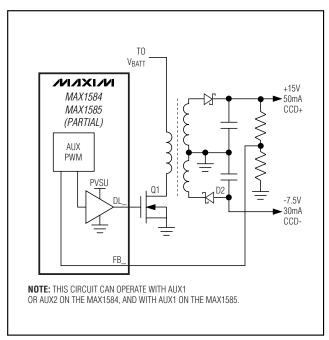

- AUX2 inverter controller (MAX1585)—Typically supplies negative CCD bias when high current is needed for large pixel-count CCDs.

- AUX3 step-down controller—Typically steps 5V generated at PVSU down to 3.3V for system logic in boost-buck designs.

### Step-Up DC-DC Converter

The step-up DC-DC switching converter is typically used to generate a 5V output voltage from a 1.5V to 4.5V battery input, but any voltage from V<sub>IN</sub> to 5V can be set. An internal NFET switch and a PFET synchronous rectifier allow conversion efficiencies as high as 95%. Under moderate to heavy loading, the converter operates in a low-noise PWM mode with constant frequency and modulated pulse width. Switching harmonics generated by fixed-frequency operation are consistent and easily filtered. Efficiency is enhanced under light (<75mA typ) loading, by an idle mode that switches the step-up only as needed to service the load. In this mode, the maximum inductor current is 250mA for each pulse.

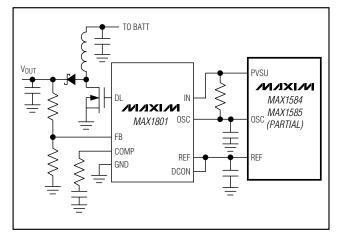

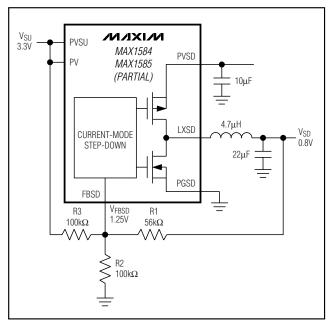

Figure 1. MAX1584/MAX1585 Typical Application for 2-Cell AA or 1-Cell Li+ Battery

M/X/W

MAX1584/MAX1585

Figure 2. MAX1584/MAX1585 Functional Diagram

### Step-Down DC-DC Converter

The step-down DC-DC converter is optimized for generating low output voltages (down to 1.25V) at high efficiency. Output voltages lower than 1V can be set by adding an additional resistor (see the *Applications Information* section). The step-down runs from the voltage at PVSD. This pin can be connected directly to the battery if sufficient headroom exists to avoid dropout; otherwise, PVSD can be powered from the output of another converter. The step-down can also operate with the step-up for boost-buck operation.

Under moderate to heavy loading, the converter operates in a low-noise PWM mode with constant frequency and modulated pulse width. Efficiency is enhanced under light (<75mA typ) loading by assuming an idle mode during which the step-down switches only as needed to service the load. In this mode, the maximum inductor current is 100mA for each pulse. The stepdown DC-DC is inactive until the step-up DC-DC is in regulation.

The step-down also features an open-drain SDOK output that goes low when the step-down output is in regulation. SDOK can be used to drive an external MOSFET switch that gates 3.3V power to the processor after the core voltage is in regulation. This connection is shown in Figure 13.

#### **Boost-Buck Operation**

The step-down input can be powered from the output of the step-up. By cascading these two channels, the step-down output can maintain regulation even as the battery voltage falls below the step-down output voltage. This is especially useful when trying to generate 3.3V from 1-cell Li+ inputs, or 2.5V from 2-cell alkaline or NiMH inputs, or when designing a power supply that must operate from both Li+ and alkaline/NiMH inputs. Compound efficiencies of up to 90% can be achieved when the step-up and step-down are operated in series.

Note that the step-up output supplies both the step-up load and the step-down input current when the stepdown is powered from the step-up. The step-down input current reduces the available step-up output current for other loads.

#### **Direct Battery Step-Down Operation**

The step-down converter can also be operated directly from the battery as long as the voltage at PVSD does not exceed PVSU by more than a Schottky diode forward voltage. When using this connection, connect an external Schottky diode from the battery input to PVSU. On the MAX1584/MAX1585, there is an internal 10k $\Omega$  resistance from PVSU to PVSD. This adds a small addi-

tional current drain (of approximately (VPVSU - VPVSD) / 10k $\Omega$ ) from PVSU when PVSD is not connected directly to PVSU.

Step-down direct battery operation improves efficiency for the step-down output (up to 95%), but restricts the upper limit of the output voltage to 200mV less than the minimum battery voltage. In 1-cell Li+ designs (with a 2.7V min), the output can be set up to 2.5V. In 2-cell alkaline or NiMH designs, the output can be limited to 1.5V or 1.8V, depending on the minimum-allowed cell voltage.

The step-down can only be briefly operated in dropout since the MAX1584/MAX1585 fault protection detects the out-of-regulation condition and activates after 100,000 OSC cycles (200ms at  $f_{OSC} = 500$ kHz). At that point, all MAX1584/MAX1585 channels shut down.

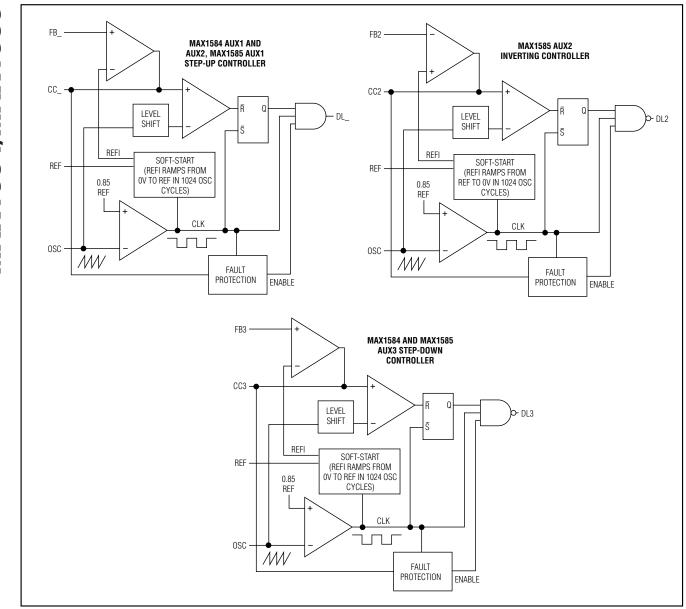

**AUX1, AUX2, and AUX3 DC-DC Controllers** The three auxiliary controllers operate as fixed-frequency voltage-mode PWM controllers. They do not have internal MOSFETs, so output power is determined by external components. The controllers regulate output voltage by modulating the pulse width of the DL\_ drive signal to an external MOSFET switch. The MAX1584

contains two step-up/flyback controllers (AUX1 and AUX2) and one step-down controller (AUX3). The MAX1585 contains one step-up controller (AUX1), one inverting controller (AUX2), and one step-down controller (AUX3).

Figure 3 shows a functional diagram of the AUX controllers. The inverting and step-down controllers differ from the step-up controllers only in the gate-drive logic and FB polarity and threshold. The sawtooth oscillator signal at OSC governs timing. At the start of each cycle, DL\_ turns on the external MOSFET switch. For step-up controllers, DL\_ goes high, while for inverting and step-down controllers, DL\_ goes low (to turn on PFETs). The external MOSFET then turns off when the internally level-shifted sawtooth rises above CC\_ or when the maximum duty cycle is exceeded. The switch remains off until the start of the next cycle. A transconductance error amplifier forms an integrator at CC\_ so that high DC loop gain and accuracy can be maintained. In step-up and step-down controllers, the FB threshold is 1.25V, and higher FB\_ voltages reduce the MOSFET duty cycle. In inverting controllers, the FB\_ threshold is OV, and lower (more negative) FB\_ voltages reduce the MOSFET duty cycle.

Auxiliary controllers do not start until the step-up DC-DC output is in regulation. If the step-up, step-down, or any of the auxiliary controllers remains faulted for 100,000

Figure 3. AUX Controller Functional Diagrams

OSC cycles, then all MAX1584/MAX1585 channels latch off.

#### Maximum Duty Cycle

The MAX1584/MAX1585 auxiliary PWM controllers have a guaranteed maximum duty cycle of 80%. In boost designs that employ continuous current, the maximum duty cycle limits the boost ratio so that:

### 1 - VIN / VOUT $\leq 80\%$

With discontinuous inductor current, no such limit exists for the input/output ratio since the inductor has time to fully discharge before the next cycle begins.

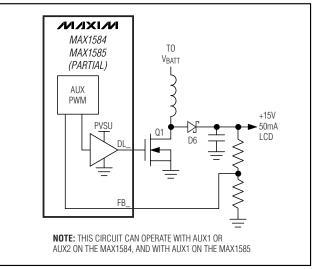

#### AUX1

AUX1 can be used for conventional DC-DC boost and flyback designs (Figure 5). Its output (DL1) is designed

MAX1584/MAX1585

to drive an N-channel MOSFET. Its feedback (FB1) threshold is 1.25V.

AUX2

In the MAX1584, AUX2 is identical to AUX1.

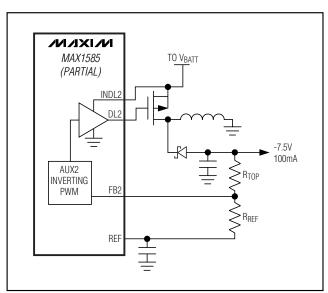

In the MAX1585, AUX2 is an inverting controller that generates a regulated negative output voltage, typically for CCD and LCD bias. This is handy in height-limited designs where transformers might not be desired.

The AUX2 MOSFET driver (DL2) in the MAX1585 is designed to drive P-channel MOSFETs. DL2 swings from GND to PVSU. See Figure 8 for a typical inverter configuration.

#### AUX3 DC-DC Step-Down Controller

AUX3 can be used for conventional DC-DC step-down (buck) designs (Figure 1). Its output (DL3) is designed to drive a P-channel MOSFET and swings from GND to PVSU. Its feedback (FB3) threshold is 1.25V.

#### **Master/Slave Configurations**

The MAX1584/MAX1585 support the MAX1801 slave PWM controllers that obtain input power, a voltage reference, and an oscillator signal directly from the MAX1584/MAX1585 master. The master/slave configuration allows channels to be easily added and minimizes system cost by eliminating redundant circuitry. The slaves also control the harmonic content of noise since their operating frequency is synchronized to that of the MAX1584/MAX1585 master converter. A MAX1801 connection to the MAX1584/MAX1585 is shown in Figure 12.

Status Outputs (SDOK, AUX10K, SCF)

The MAX1584/MAX1585 include three versatile status outputs that can provide information to the system. All are open-drain outputs and can directly drive MOSFET switches to facilitate sequencing, disconnect loads during overloads, or perform other hardware-based functions.

**SDOK** pulls low when the step-down has successfully completed soft-start. SDOK goes high impedance in shutdown, overload, and thermal limit. A typical use for SDOK is to enable 3.3V power to the CPU I/O after the CPU core is powered up (Figure 13), thus providing safe sequencing in hardware without system intervention.

**AUX10K** pulls low when the AUX1 controller has successfully completed soft-start. AUX10K goes high impedance in shutdown, overload, and thermal limit. A typical use for AUX10K is to drive a P-channel MOSFET that gates 5V power to the CCD until the +15V CCD bias (generated by AUX1) is powered up (Figure 14).

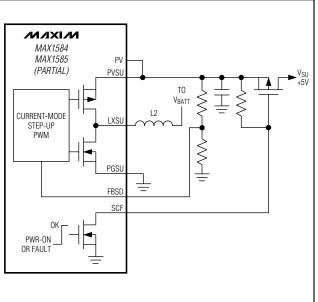

**SCF** goes high (high impedance, open drain) when overload protection occurs. Under normal operation, SCF pulls low. SCF can drive a high-side P-channel MOSFET switch that can disconnect a load during power-up or when a channel turns off in response to a logic command or an overload. Several connections are possible for SCF. One is shown in Figure 15, where SCF provides load disconnect for the step-up on fault and power-up.

#### Soft-Start

The MAX1584/MAX1585 channels feature a soft-start function that limits inrush current and prevents excessive battery loading at startup by ramping the output voltage of each channel up to the regulation voltage. This is accomplished by ramping the internal reference inputs to each channel error amplifier from 0V to the 1.25V reference voltage over a period of 4096 oscillator cycles (16ms at 500kHz) when initial power is applied or when a channel is enabled. Soft-start is not included in the step-up converter in order to avoid limiting start-up capability with loading.

The step-down soft-start ramp takes half the time (2048 clock cycles) of the other channel ramps. This allows the step-down and AUX3 output (when set to 3.3V) to track each other and rise at nearly the same dV/dt rate on power-up. Once the step-down output reaches its regulation point (1.5V or 1.8V typ), the AUX3 output (3.3V typ) continues to rise at the same ramp rate.

#### **Fault Protection**

The MAX1584/MAX1585 have robust fault and overload protection. After power-up, the device is set to detect an out-of-regulation state that could be caused by an overload or short. If any DC-DC converter channel (step-up, step-down, or any of the auxiliary controllers) remains faulted for 100,000 clock cycles (200ms at 500kHz), then **all** outputs latch off until the step-up DC-DC converter is reinitialized by the ONSU pin or by cycling the input power. The fault-detection circuitry for any channel is disabled during its initial turn-on soft-start sequence.

An exception to the standard fault behavior is that there is no 100,000 clock-cycle delay in entering the fault state if the step-up output (PVSU) is dragged below its 2.5V UVLO threshold or is shorted. The step-up UVLO immediately triggers and shuts down all channels. The step-up then continues to attempt to start. If the step-up output short remains, these attempts do not succeed since PVSU remains near ground.

If a soft-short or overload remains on PVSU, the startup oscillator switches the internal N-channel MOSFET, but fault is retriggered if regulation is not achieved by the

Figure 4. Oscillator Functional Diagram

MAX1584/MAX1585

end of the soft-start interval. If PVSU is dragged below the input, the overload is supplied by the body diode of the internal synchronous rectifier or by a Schottky diode connected from the battery to PVSU. If desired, this overload current can be interrupted by a P-channel MOSFET controlled by SCF, as shown in Figure 15.

#### Reference

The MAX1584/MAX1585 have internal 1.250V references. Connect a  $0.1\mu$ F ceramic bypass capacitor from REF to GND within 0.2in (5mm) of the REF pin. REF can source up to 200µA and is enabled when ONSU is high and PVSU is above 2.5V. The auxiliary controllers and MAX1801 slave controllers (if connected) each sink up to 30µA REF current during startup. If the application requires that REF be loaded beyond 200µA, buffer REF with a unity-gain amplifier or op amp.

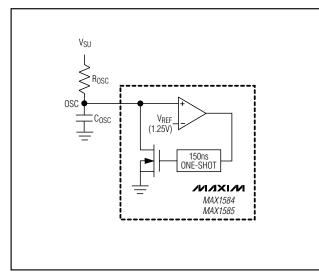

### Oscillator

All MAX1584/MAX1585 DC-DC converter channels employ fixed-frequency PWM operation. The operating frequency is set by an RC network at the OSC pin. The range of usable settings is 100kHz to 1MHz. When MAX1801 slave controllers are added, they operate at the frequency set by OSC.

The oscillator uses a comparator, a 150ns one-shot, and an internal NFET switch in conjunction with an external timing resistor and capacitor (Figure 4). When the switch is open, the capacitor voltage exponentially approaches the step-up output voltage from zero with a time constant given by the product of R<sub>OSC</sub> and C<sub>OSC</sub>. The comparator output switches high when the capacitor voltage reaches V<sub>REF</sub> (1.25V). In turn, the one-shot

Figure 5. +15V LCD Bias with Basic Boost Topology

activates the internal MOSFET switch to discharge the capacitor within a 150ns interval, and the cycle repeats. The oscillation frequency changes as the main output voltage ramps upward following startup. The oscillation frequency is then constant once the main output is in regulation.

### Low-Voltage Startup Oscillator

The MAX1584/MAX1585 internal control and referencevoltage circuitry receive power from PVSU and do not function when PVSU is less than 2.5V. To ensure lowvoltage startup, the step-up employs a low-voltage startup oscillator that activates at 0.9V if a Schottky rectifier is connected from V<sub>BATT</sub> to PVSU (1.1V with no Schottky rectifier). The startup oscillator drives the internal N-channel MOSFET at LXSU until PVSU reaches 2.5V, at which point voltage control is passed to the current-mode PWM circuitry.

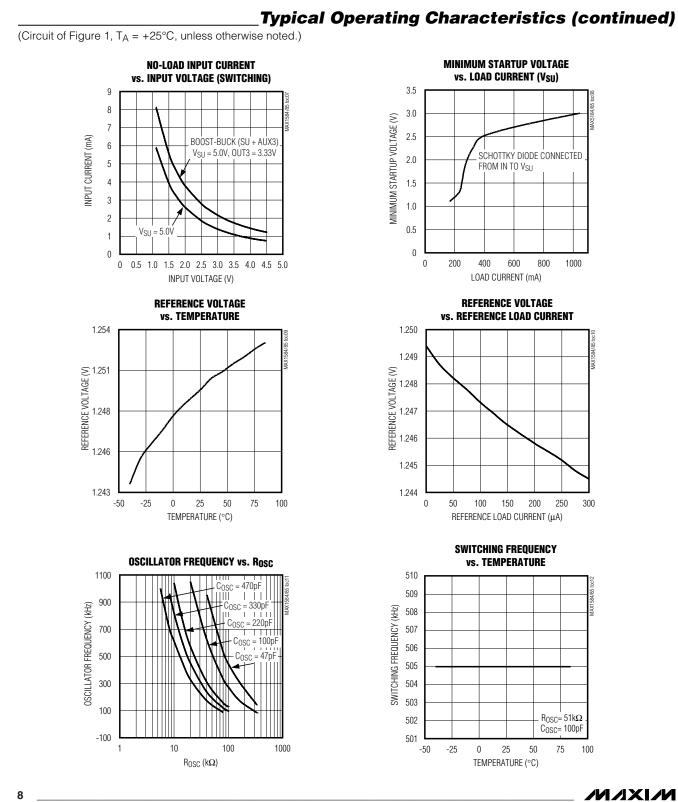

Once in regulation, the MAX1584/MAX1585 operate with inputs as low as 0.7V since internal power for the IC is supplied by PVSU. At low input voltages, the stepup can have difficulty starting into heavy loads (see the Minimum Startup Voltage vs. Load Current graph in the *Typical Operating Characteristics* section); however, this can be remedied by connecting an external Pchannel load switch driven by SCF so the load is not connected until the PVSU is in regulation (Figure 15).

### **ON\_ Control Inputs**

The step-up converter activates with a high input at ONSU. The step-down and auxiliary DC-DC converters 1, 2, and 3 activate with a high input at ONSD, ON1, ON2, and ON3, respectively. The step-down and auxil-

iary converters and cannot be activated until PVSU is in regulation. For automatic startup, connect ON\_ to PVSU or a logic level greater than 1.6V.

### \_Design Procedure

#### **Setting the Switching Frequency**

Choose a switching frequency to optimize external component size or circuit efficiency for the particular application. Typically, switching frequencies between 400kHz and 500kHz offer a good balance between component size and circuit efficiency—higher frequencies generally allow smaller components, and lower frequencies give better conversion efficiency. The switching frequency is set with an external timing resistor (Rosc) and capacitor (Cosc). At the beginning of a cycle, the timing capacitor charges through the resistor until it reaches VREF. The charge time, t<sub>1</sub>, is as follows:

$t_1 = -R_{OSC} \times C_{OSC} \times I_n(1 - 1.25 / V_{PVSU})$

The capacitor voltage then decays to zero over time  $t_2$  = 150ns. The oscillator frequency is as follows:

$$f_{OSC} = 1 / (t_1 + t_2)$$

fOSC can be set from 100kHz to 1MHz. Choose COSC between 22pF and 470pF. Determine ROSC:

$R_{OSC} = (150ns - 1 / f_{OSC}) / (C_{OSC} \times I_n[1 - 1.25])$

Vpvsu])

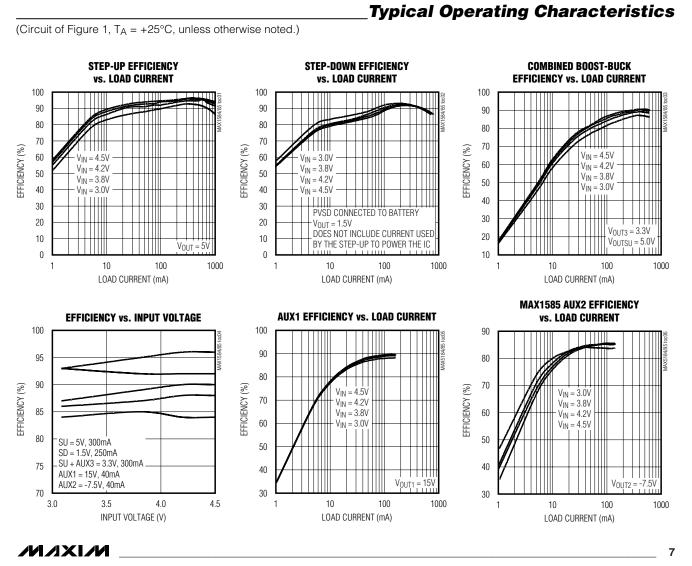

See the *Typical Operating Characteristics* section for fosc vs. Rosc using different values of Cosc.

#### **Setting Output Voltages**

The MAX1584/MAX1585 step-up and step-down converters and the AUX1 controllers have resistoradjustable output voltages. When setting the voltage for all channels except AUX2 on the MAX1585, connect a resistive voltage-divider from the output voltage to the corresponding FB\_ input. The FB\_ input bias current is less than 100nA, so choose the low-side (FB\_-to-GND) resistor (RL) to be 100k $\Omega$  or less. Then calculate the high-side (output-to-FB\_) resistor (R<sub>H</sub>):

$R_{H} = R_{L} [(V_{OUT} / 1.25) - 1]$

AUX2 is an inverter on the MAX1585, so the FB2 threshold on the MAX1585 is 0V. To set the MAX1585 AUX2 negative output voltage, connect a resistive voltage-divider from the negative output to the FB2 input, and then to REF. The FB2 input bias current is less than 100nA, so choose the REF-side (FB2-to-REF) resistor (R<sub>REF</sub>) to be 100k $\Omega$  or less. Then calculate the top-side (negative output-to-FB2) resistor:

RTOP = RREF (-VOUT(AUX2) / 1.25)

### **General Filter-Capacitor Selection**

The input capacitor in a DC-DC converter reduces current peaks drawn from the battery or other input power source and reduces switching noise in the controller. The impedance of the input capacitor at the switching frequency should be less than that of the input source so high-frequency switching currents do not pass through the input source.

The output capacitor keeps output ripple small and ensures control-loop stability. The output capacitor must also have low impedance at the switching frequency. Ceramic, polymer, and tantalum capacitors are suitable, with ceramic exhibiting the lowest ESR and high-frequency impedance.

Output ripple with a ceramic output capacitor is approximately:

VRIPPLE =  $I_L(PEAK) [1 / (2\pi \times fOSC \times COUT)]$

If the capacitor has significant ESR, the output ripple component due to capacitor ESR is:

$V_{RIPPLE(ESR)} = I_{L(PEAK)} \times ESR$

Output capacitor specifics are also discussed in each converter's *Compensation* section.

#### **Step-Up Component Selection**

The external components required for the step-up are an inductor, an input and output filter capacitor, and a compensation RC.

The inductor is typically selected to operate with continuous current for best efficiency. An exception might be if the step-up ratio, (V<sub>OUT</sub> / V<sub>IN</sub>), is greater than 1 / (1 - D<sub>MAX</sub>), where D<sub>MAX</sub> is the maximum PWM duty factor of 80%.

When using the step-up channel to boost from a low input voltage, loaded startup is aided by connecting a Schottky diode from the battery to PVSU. See the Minimum Startup Voltage vs. Load Current graph in the *Typical Operating Characteristics* section.

#### Step-Up Inductor

In most step-up designs, a reasonable inductor value  $(L_{IDEAL})$  can be derived from the following equation, which sets continuous peak-to-peak inductor current at half the DC inductor current:

$LIDEAL = [2VIN(MAX) \times D(1 - D)] / (IOUT \times fOSC)$

where D is the duty factor given by:

$$D = 1 - (V_{IN} / V_{OUT})$$

Given L<sub>IDEAL</sub>, the consistent peak-to-peak inductor current is  $0.5 \times I_{OUT} / (1 - D)$ . The peak inductor current is as follows:

$I_{IND(PK)} = 1.25 \times I_{OUT} / (1 - D)$

Inductance values smaller than LIDFAL can be used to reduce inductor size; however, if much smaller values are used, inductor current rises and a larger output capacitance might be required to suppress output ripple.

### Step-Up Compensation

The inductor and output capacitor are usually chosen first in consideration of performance, size, and cost. The compensation resistor and capacitor are then chosen to optimize control-loop stability. In some cases, it helps to readjust the inductor or output capacitor value to get optimum results. For typical designs, the component values in the circuit of Figure 1 yield good results.

The step-up converter employs current-mode control, thereby simplifying the control-loop compensation. When the converter operates with continuous inductor current (typically the case), a right-half-plane zero appears in the loop-gain frequency response. To ensure stability, the control-loop gain should cross over (drop below unity gain) at a frequency (fc) much less than that of the right-half-plane zero.

The relevant characteristics for step-up channel compensation are as follows:

- Transconductance (from FBSU to CCSU), gMEA (135µS)

- Current-sense amplifier transresistance, R<sub>CS</sub> (0.3V/A)

- Feedback regulation voltage, VFB (1.25V)

- Step-up output voltage, V<sub>SU</sub>, in V

- Output load equivalent resistance, RIDAD, in  $\Omega = VSUOUT / ILOAD$

The key steps for step-up compensation are as follows:

- 1) Place fc sufficiently below the right-half-plane zero (RHPZ) and calculate Cc.

- 2) Select R<sub>C</sub> based on the allowed load-step transient. Rc sets a voltage delta on the Cc pin that corresponds to load-current step.

- 3) Calculate the output-filter capacitor (COUT) required to allow the R<sub>C</sub> and C<sub>C</sub> selected.

- 4) Determine if  $C_P$  is required (if calculated to be >10pF).

For continuous conduction, the right-half-plane zero frequency (f<sub>RHPZ</sub>) is given by the following:

RHPZ = VSUOUT (1 - D)<sup>2</sup> / (

$$2\pi \times L \times I_{LOAD}$$

)

where D = the duty cycle = 1 -  $(V_{IN} / V_{OUT})$ , L is the inductor value, and ILOAD is the maximum output current. Typically, target crossover (f<sub>C</sub>) for 1/6 of the RHPZ. For example, if we assume  $f_{OSC} = 500$ kHz, V<sub>IN</sub> = 2.5V,  $V_{OUT}$  = 5V, and  $I_{OUT}$  = 0.5A, then  $R_{LOAD}$  = 10 $\Omega$ . If we select L = 4.7 $\mu$ H, then:

$f_{RHPZ} = 5 (2.5 / 5)^2 / (2\pi \times 4.7 \times 10^{-6} \times 0.5) = 84.65 \text{kHz}$

Choose  $f_{C} = 14$ kHz. Calculate C<sub>C</sub>:

$C_{C} = (V_{FB} / V_{OUT})(R_{LOAD} / R_{CS})(g_{M} / 2\pi \times f_{C})(1 - D)$ = (1.25 / 5)(10 / 0.3) x (135µS / (6.28 x 14kHz) (2/5) = 6.4 nF

Choose 6.8nF.

Now select R<sub>C</sub> so transient-droop requirements are met. As an example, if 4% transient droop is allowed, the input to the error amplifier moves 0.04 x 1.25V, or 50mV. The error-amp output drives 50mV x 135µS, or 6.75µA across R<sub>C</sub> to provide transient gain. Since the current-sense transresistance is 0.3V/A, the value of R<sub>C</sub> that allows the required load step swing is as follows:

$$R_{C} = 0.3 I_{IND(PK)} / 6.75 \mu A$$

In a step-up DC-DC converter, if LIDEAL is used, output current relates to inductor current by:

$$I_{IND(PK)} = 1.25 \times I_{OUT} / (1 - D) = 1.25 \times I_{OUT} \times V_{OUT} / V_{IN}$$

So for a 500mA output load step with  $V_{IN} = 2.5V$  and  $V_{OUT} = 5V$ :

$$R_C = [1.25(0.3 \times 0.5 \times 5) / 2)] / 6.75 \mu A = 69.4 k\Omega$$

Note that the inductor does not limit the response in this case since it can ramp at 2.5V / 4.7µH, or 530mA/µs.

The output filter capacitor is then chosen so the COUT RLOAD pole cancels the RC CC zero:

$COUT \times RLOAD = RC \times CC$

For the example:

$$C_{OUT} = 68k\Omega \times 6.8nF / 10\Omega = 46\mu F$$

Choose 47µF for COUT. If the available COUT is substantially different from the calculated value, insert the available COUT value into the above equation and recalculate Rc. Higher substituted COUT values allow a higher R<sub>C</sub>, which provides higher transient gain and consequently less transient droop.

If the output filter capacitor has significant ESR, a zero occurs at the following:

$$Z_{ESR} = 1 / (2\pi \times C_{OUT} \times R_{ESR})$$

If  $Z_{ESR} > f_C$ , it can be ignored, as is typically the case with ceramic output capacitors. If  $Z_{ESR}$  is less than  $f_C$ , it should be cancelled with a pole set by capacitor CP connected from CCSU to GND:

$C_P = C_{OUT} \times R_{ESR} / R_C$

If  $C_P$  is calculated to be <10pF, it can be omitted.

#### **Step-Down Component Selection**

#### Step-Down Inductor

The external components required for the step-down are an inductor, input and output filter capacitors, and a compensation RC network.