#### **General Description**

The MAX1874 charges a single-cell Li+ battery from both USB and AC adapter sources. It also includes battery-to-input power switchover, so the system can be powered directly from the power source rather than from the battery.

In its simplest application, the MAX1874 needs no external MOSFET or diodes, and accepts input voltages up to 6.5V; however, DC input overvoltage protection up to 18V can be added with a single SOT PFET.

On-chip thermal limiting simplifies PC board layout and allows optimum charging rate without the thermal limits imposed by worst-case battery and input voltage. When the MAX1874 thermal limit is reached, the charger does not shut down but simply reduces charging current.

Ambient or battery temperature can be monitored with an external thermistor. When the temperature is out of range, charging pauses.

Other features include a CHG output to indicate when battery current tapers below a predetermined level. DC power-OK (DCOK), USB power-OK (UOK), and poweron (PON) outputs indicate when valid power is present. These outputs drive logic or power-selection MOSFETs to disconnect the charging sources from the load and to protect the MAX1874 from overvoltage.

The MAX1874 contains no logic for communication with the USB host. It must receive instructions from a local microcontroller. The MAX1874 is available in a 16-pin 5mm × 5mm thin QFN package and operates over the -40°C to +85°C temperature range.

### **Applications**

**PDAs** Cell Phones Digital Cameras Wireless Appliances

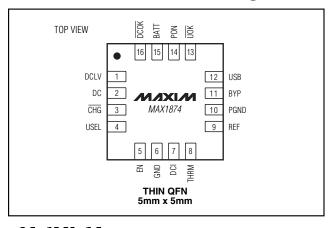

### Pin Configuration

#### **Features**

- ♦ Charge from USB\* or AC Adapter

- ♦ Automatic Switchover to AC Adapter

- ♦ Thermal Limiting Simplifies Board Design

- ♦ Small, High-Power 16-Pin Thin QFN Package

- ♦ Input Protection Up to 18V

- ♦ Soft-Start

- ♦ Automatic Battery-to-Input Load Switch

\*Protected by U.S. Patent #6,507,172.

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE           |

|------------|----------------|-----------------------|

| MAX1874ETE | -40°C to +85°C | 16 Thin QFN 5mm x 5mm |

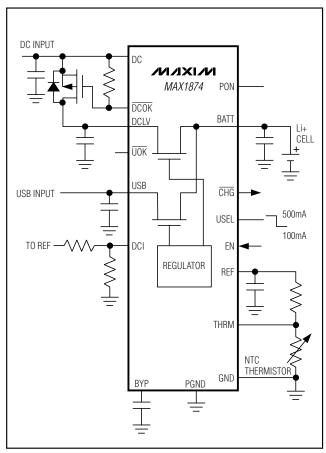

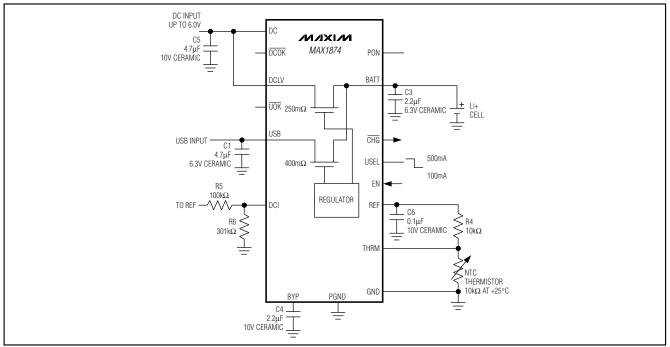

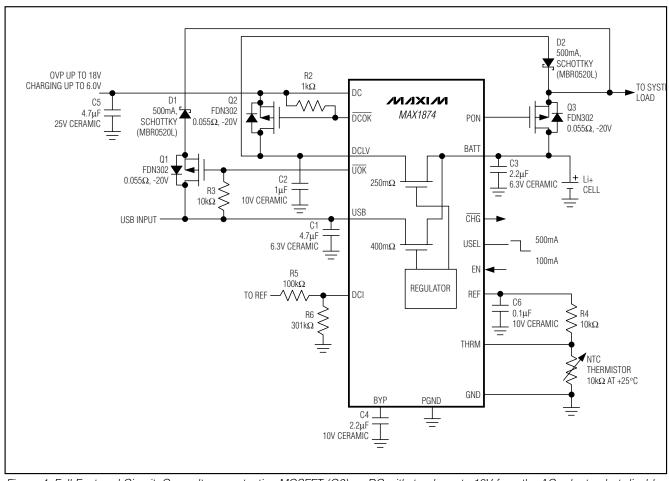

### Typical Operating Circuit

Functional Diagram appears at the end of the data sheet.

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| 0.3V to +20V  |

|---------------|

| RM,           |

| 0.3V to +7V   |

| 0.3V to +0.3V |

| 1.1A          |

| 0.6A          |

|               |

| Continuous Power Dissipation ( $T_A = +$ | -70°C)         |

|------------------------------------------|----------------|

| 16-Pin 5mm × 5mm Thin QFN                |                |

| (derate 21.3mW/°C above +70°C)           | 1.7W           |

| Operating Temperature Range              | 40°C to +85°C  |

| Storage Temperature Range                | 65°C to +150°C |

| Maximum Junction Temperature             | +150°C         |

| Lead Temperature (soldering, 10s)        | +300°C         |

| Maximum Junction Temperature             | +150°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VUSB = VDC = VDCLV = VEN = VUSEL = 5V, VBATT = 4.2V, VTHRM = VREF / 2, Circuit of Figure 2,  $T_A = 0$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                                                  | CONDITIONS                                                                                                                  | MIN    | TYP  | MAX    | UNITS |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|------|--------|-------|

| INPUT VOLTAGE RANGES AND INPU                              | T CURRENT                                                                                                                   | •      |      |        |       |

| Maximum DC Input Voltage with<br>Overvoltage Protection    | Q2 input MOSFET must be in place; charging occurs only below 6.2V, Figures 3, 4, and 5                                      |        |      | 18     | V     |

| Maximum DC Input Voltage Without<br>Overvoltage Protection | DC = DCLV, Q2 input MOSFET not on circuit, Figure 2                                                                         |        |      | 6.5    | V     |

| Maximum Input Voltage for Charging                         | nput Voltage for Charging                                                                                                   |        | 6.2  | 6.5    | V     |

| DC Cupply Current                                          | V <sub>EN</sub> = 0V                                                                                                        |        | 2    | 4      | mA    |

| DC Supply Current                                          | $V_{EN} = 5V$                                                                                                               |        | 4    | 6      | ША    |

| DCLV Operating Voltage Range                               |                                                                                                                             | 4.35   |      | 6.00   | V     |

| DCLV Shutdown Supply Current                               | V <sub>EN</sub> = 0V                                                                                                        |        | 300  | 500    | μΑ    |

| USB Input Voltage Range                                    |                                                                                                                             | 4.35   |      | 6.50   | V     |

|                                                            | V <sub>EN</sub> = 0V                                                                                                        |        | 500  | 750    | μΑ    |

| JSB Supply Current                                         | $V_{EN} = 5V$ , $V_{DC} = 0V$                                                                                               |        | 2    | 3      | mA    |

|                                                            | $V_{EN} = 5V$ , $V_{DC} = 5V$                                                                                               |        | 160  | 300    | μΑ    |

| DCI Input Current                                          |                                                                                                                             |        | 1    | 100    | nA    |

| BYP Output Resistance                                      | (Note 1)                                                                                                                    |        | 5    |        | Ω     |

| THRM Input Bias Current                                    |                                                                                                                             |        | 1    | 100    | nA    |

| BATTERY VOLTAGE                                            |                                                                                                                             |        |      |        |       |

| BATT Regulation Voltage                                    |                                                                                                                             | 4.1685 | 4.20 | 4.2315 | V     |

| BATT Prequal Voltage Threshold                             | BATT rising                                                                                                                 | 2.8    | 3    | 3.2    | V     |

| Prequal Threshold Hysteresis                               |                                                                                                                             |        | 70   |        | mV    |

| LICD Charging Handrage                                     | I <sub>USB</sub> = 100mA                                                                                                    |        | 100  |        | \/    |

| USB Charging Headroom                                      | I <sub>USB</sub> = 500mA                                                                                                    |        | 200  |        | mV    |

| DC Charging Headroom                                       | I <sub>DCIN</sub> = 800mA                                                                                                   |        | 250  |        | mV    |

| REF Voltage (Buffered Output)                              | I <sub>REF</sub> = 0 to 500μA, 4V < V <sub>DC</sub> or V <sub>USB</sub> < 6.5V;<br>does not affect BATT regulation accuracy | 2.94   | 3    | 3.06   | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = V_{USEL} = 5V, V_{BATT} = 4.2V, V_{THRM} = V_{REF} / 2$ , Circuit of Figure 2,  $T_A = 0$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                               | CONDITIONS                                                      | MIN                  | TYP             | MAX              | UNITS            |

|-----------------------------------------|-----------------------------------------------------------------|----------------------|-----------------|------------------|------------------|

| BATTERY CHARGING AND PRECHAR            | GE CURRENT                                                      | •                    |                 |                  | •                |

| DCI Voltage Range                       |                                                                 | 0.1 x V <sub>F</sub> | REF             | V <sub>REF</sub> | V                |

| DOLVelte de to DATT Comment             | V <sub>DCI</sub> = V <sub>REF</sub>                             | 950                  | 1000            | 1050             | A                |

| DCI Voltage to BATT Current             | V <sub>DCI</sub> = V <sub>REF</sub> / 2                         | 490                  | 520             | 550              | mA               |

| LICE Charging Current                   | USEL = high                                                     |                      | 455             | 495              | m ^              |

| USB Charging Current                    | USEL = low                                                      |                      | 82              | 95               | mA               |

| Soft-Start Current-Ramp Time            | Measured from 10% to 90%                                        |                      | 7               |                  | ms               |

| Prequal Charging Current                | $V_{BATT} = 2.5V$                                               | 35                   | 55              | 70               | mA               |

| BATT Input Current                      | No DC or USB power, V <sub>BATT</sub> = 4.2V                    |                      | 5               | 7.5              | μΑ               |

| BATT Shutdown Current                   | EN = GND, USB- and/or DC-powered                                |                      | 1               | 2                | μΑ               |

| THERMISTOR MONITOR AND DIE-TEM          | IPERATURE REGULATION                                            |                      |                 |                  |                  |

| THRM COLD Trip Level                    | (Note 2)                                                        | 0.72                 | 0.74            | 0.76             | V <sub>REF</sub> |

| THRM HOT Trip Level                     | (Note 2)                                                        | 0.28                 | 0.29            | 0.30             | V <sub>REF</sub> |

| THRM Disable Threshold                  |                                                                 | 50                   | 100             | 150              | mV               |

| Internal Die Thermal Limit              |                                                                 |                      | +105            |                  | °C               |

| LOGIC INPUT/OUTPUTS AND GATE D          | RIVERS                                                          |                      |                 |                  |                  |

| PON High Output Resistance              | PON pulled up to active input (DCLV or USB), VDCLV or VUSB = 5V |                      | 25              |                  | Ω                |

| PON Low Output Resistance               | PON resistance to GND, V <sub>DCLV</sub> = V <sub>USB</sub> = 0 |                      | 120             |                  | kΩ               |

| DCOK Low Output Resistance              | DCOK pulled low                                                 |                      | 25              |                  | Ω                |

| DCOK Off-Leakage Current                | $V_{\overline{DCOK}} = 12V, V_{\overline{DC}} = 0V$             |                      |                 | 1                | μA               |

| UOK Output Resistance                   | UOK resistance to GND, V <sub>DC</sub> = 0                      |                      | 25              |                  | Ω                |

| UOK Off-Leakage Current                 | V <del>∪OK</del> = 6.5V                                         |                      |                 | 1                | μΑ               |

|                                         | DC input (% of charge current set at DCI)                       | 8                    | 12.5            | 19               |                  |

| CHG Threshold to Indicate Battery Full, | USB input, USEL = 5V (% of USB charging current)                | 20                   | 25              | 30               | 0/               |

| Battery Current Falling (Note 3)        | USB input with USEL = 0                                         |                      | Voltage<br>mode |                  | - %              |

| CHG Logic-Low Output                    | Sinking 10mA sink                                               |                      |                 | 0.4              | V                |

| CHG Leakage Current                     | V <del>CHG</del> = 6.5V                                         |                      |                 | 1                | μΑ               |

| EN, USEL Logic-Input High Level         |                                                                 | 1.6                  |                 |                  | V                |

| EN, USEL Logic-Input Low Level          |                                                                 |                      |                 | 0.4              | V                |

| EN, USEL Input Bias Current             |                                                                 |                      |                 | 1                | μΑ               |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = V_{USEL} = 5V, V_{BATT} = 4.2V, V_{THRM} = V_{REF} / 2$ , Circuit of Figure 2,  $T_A = 0$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                                                | CONDITIONS                                                                       | MIN TYP MAX | UNITS |

|----------------------------------------------------------|----------------------------------------------------------------------------------|-------------|-------|

| TIMING                                                   |                                                                                  |             |       |

| DC Rising to DCOK Falling                                | USB = open, DC rising to 5V                                                      | 20          | ms    |

| USB Rising to UOK Falling                                | DC = open, USB rising to 5V                                                      | ms          |       |

| DC Falling to DCOK Going Open-Drain Propagation Delay    | USB = open, $1k\Omega$ pullup                                                    | μs          |       |

| USB Falling to UOK Going<br>Open-Drain Propagation Delay | DC = open, $10k\Omega$ pullup 2                                                  |             | μs    |

| DC Rising to PON Rising (90%)                            | USB = open, DC step to 5V, BATT = 3.6V, 100kΩ pulldown 20                        |             | ms    |

| USB Rising to PON Rising (90%)                           | DC = open, V <sub>USB</sub> step to 5V, V <sub>BATT</sub> = 3.6V, 100kΩ pulldown |             | ms    |

| DC Falling to PON Going<br>Open-Drain Propagation Delay  | USB = open, 100k $\Omega$ pulldown                                               | 2           | μs    |

| USB Falling to PON Going<br>Open-Drain Propagation Delay | DC = open, $100k\Omega$ pulldown                                                 | 2           | μs    |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = V_{USEL} = 5V, V_{BATT} = 4.2V, V_{THRM} = V_{REF} / 2$ , Circuit of Figure 2, **T<sub>A</sub> = -40°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 4)

| PARAMETER                                                  | CONDITIONS                                                                             | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|------|-------|

| INPUT VOLTAGE RANGES AND INPUT                             | CURRENT                                                                                |      |     |      |       |

| Maximum DC Input Voltage with<br>Overvoltage Protection    | Q2 input MOSFET must be in place; charging occurs only below 6.2V, Figures 3, 4, and 5 |      |     | 18   | V     |

| Maximum DC Input Voltage Without<br>Overvoltage Protection | DC = DCLV, Q2 input MOSFET not on circuit, Figure 3                                    |      |     | 6.5  | V     |

| Maximum Input Voltage for Charging                         |                                                                                        | 6.0  |     | 6.5  | V     |

| DC Cumply Current                                          | $V_{EN} = 0V$                                                                          |      |     | 4    | mA    |

| DC Supply Current                                          | $V_{EN} = 5V$                                                                          |      |     | 6    | IIIA  |

| DCLV Operating Voltage Range                               |                                                                                        | 4.35 |     | 6.00 | V     |

| DCLV Shutdown Supply Current                               | $V_{EN} = 0V$                                                                          |      |     | 500  | μΑ    |

| USB Input Voltage Range                                    |                                                                                        | 4.35 |     | 6.50 | V     |

|                                                            | $V_{EN} = 0V$                                                                          |      |     | 750  | μA    |

| USB Supply Current                                         | $V_{EN} = 5V$ , $V_{DC} = 0V$                                                          |      |     | 3    | mA    |

|                                                            | $V_{EN} = 5V$ , $V_{DC} = 5V$                                                          |      |     | 300  | μΑ    |

| DCI Input Current                                          |                                                                                        |      |     | 100  | nA    |

| THRM Input Bias Current                                    |                                                                                        |      |     | 100  | nA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = V_{USEL} = 5V, V_{BATT} = 4.2V, V_{THRM} = V_{REF} / 2, Circuit of Figure 2, \textbf{T}_{\textbf{A}} = \textbf{-40}^{\circ}\textbf{C} \text{ to } \textbf{+85}^{\circ}\textbf{C}, \text{ unless otherwise noted. Typical values are at } T_{A} = \textbf{+25}^{\circ}\textbf{C}.) \text{ (Note 4)}$

| PARAMETER                                                                   | CONDITIONS                                                                                                               | MIN TY                 | P MAX     | UNITS            |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|------------------|

| BATTERY VOLTAGE                                                             |                                                                                                                          | •                      |           |                  |

| BATT Regulation Voltage                                                     |                                                                                                                          | 4.1685                 | 4.2315    | V                |

| BATT Prequal Voltage Threshold                                              | BATT rising                                                                                                              | 2.8                    | 3.2       | V                |

| REF Voltage (Buffered Output)                                               | I <sub>REF</sub> = 0 to 500μA, 4V < V <sub>DC</sub> or V <sub>USB</sub> < 6.5V; does not affect BATT regulation accuracy | 2.94                   | 3.06      | ٧                |

| BATTERY CHARGING AND PRECHAR                                                | GE CURRENT                                                                                                               |                        |           |                  |

| DCI Voltage Range                                                           |                                                                                                                          | 0.1 x V <sub>REF</sub> | $V_{REF}$ | V                |

| DCI Voltage to BATT Current                                                 | V <sub>DCI</sub> = V <sub>REF</sub>                                                                                      | 930                    | 1070      | m ^              |

| DCI Voltage to BATT Current                                                 | V <sub>DCI</sub> = V <sub>REF</sub> / 2                                                                                  | 490                    | 565       | mA               |

| LICE Charaina Current                                                       | USEL = high                                                                                                              |                        | 495       | <b>~</b> ^       |

| USB Charging Current                                                        | USEL = low                                                                                                               |                        | 95        | mA               |

| Prequal Charging Current                                                    | V <sub>BATT</sub> = 2.5V                                                                                                 | 40                     | 70        | mA               |

| BATT Input Current                                                          | No DC or USB power, V <sub>BATT</sub> = 4.2V                                                                             |                        | 7.5       | μΑ               |

| BATT Shutdown Current                                                       | EN = GND, USB and/or DC powered                                                                                          |                        | 2         | μΑ               |

| THERMISTOR MONITOR AND DIE-TEN                                              | IPERATURE REGULATION                                                                                                     |                        |           |                  |

| THRM COLD Trip Level                                                        | (Note 2)                                                                                                                 | 0.72                   | 0.76      | $V_{REF}$        |

| THRM HOT Trip Level                                                         | (Note 2)                                                                                                                 | 0.28                   | 0.30      | V <sub>REF</sub> |

| THRM Disable Threshold                                                      |                                                                                                                          | 50                     | 150       | mV               |

| LOGIC INPUT/OUTPUTS AND GATE D                                              | RIVERS                                                                                                                   |                        |           |                  |

| DCOK Off-Leakage Current                                                    | $V_{\overline{DCOK}} = 12V, V_{DC} = 0V$                                                                                 |                        | 1         | μΑ               |

| UOK Off-Leakage Current                                                     | $V_{\overline{UOK}} = 6.5V$                                                                                              |                        | 1         | μΑ               |

|                                                                             | DC input (% of charge current set at DCI)                                                                                | 8                      | 20        |                  |

| CHG Threshold to Indicate Battery Full,<br>Battery Current Falling (Note 3) | USB input, USEL = 5V<br>(% of USB charging current)                                                                      | 20                     | 30        | %                |

| CHG Logic-Low Output                                                        | Sinking 10mA sink                                                                                                        |                        | 0.4       | V                |

| CHG Leakage Current                                                         | V <sub>CHG</sub> = 6.5V                                                                                                  |                        | 1         | μΑ               |

| EN, USEL Logic-Input High Level                                             |                                                                                                                          | 1.6                    |           | V                |

| EN, USEL Logic-Input Low Level                                              |                                                                                                                          |                        | 0.4       | V                |

| EN, USEL Input Bias Current                                                 |                                                                                                                          |                        | 1         | μΑ               |

- Note 1: BYP internally connects to the active power input (DCLV or USB). DCLV takes priority if both inputs are powered.

- Note 2: These limits guarantee +5°C accuracy with 5% accuracy of thermistor beta (3450 nominal) with 2°C of hysteresis.

- **Note 3:** The CHG output does not go high unless charge current is below the indicated threshold (as set by DCI) and the charger is in voltage-mode operation. In 100mA USB mode, CHG goes high when the charger transitions from current to voltage mode.

- **Note 4:** Specifications to -40°C are guaranteed by design, not production tested.

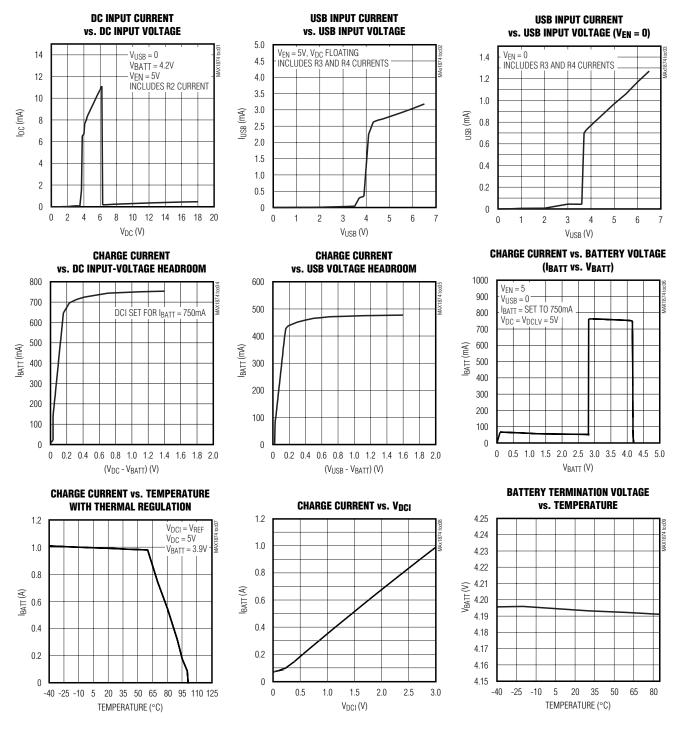

### **Typical Operating Characteristics**

$(V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = 5V, V_{BATT} = 4.2V, V_{THRM} = V_{REF} / 2, V_{DCI} = V_{REF}, V_{USEL} = 5V, Circuit of Figure 4, T_A = +25°C, unless otherwise noted.)$

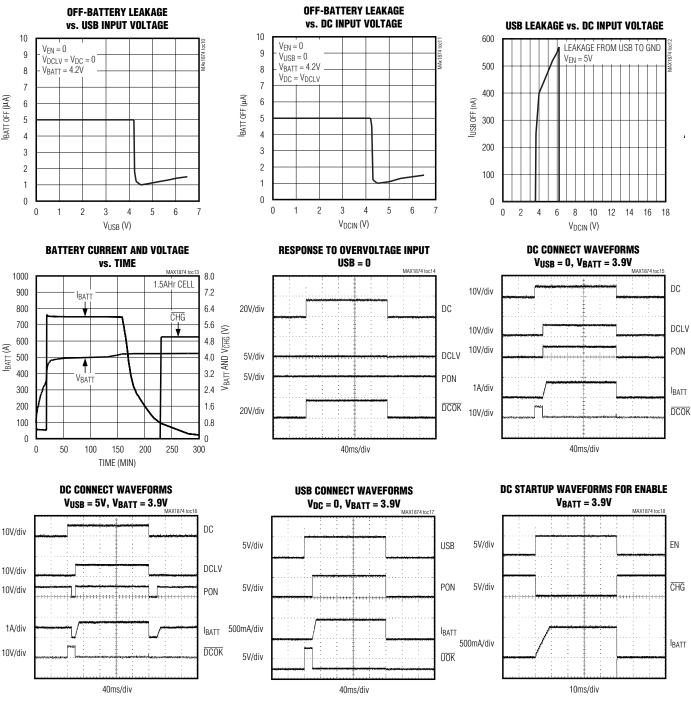

### Typical Operating Characteristics (continued)

(VUSB = VDC = VDCLV = VEN = 5V, VBATT = 4.2V, VTHRM = VREF / 2, VDCI = VREF, VUSEL = 5V, Circuit of Figure 4, TA = +25°C, unless otherwise noted.)

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                               |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DCLV | Low-Voltage Charger Input. DCLV charges BATT through an internal MOSFET. Maximum operating voltage at this pin is 6.0V. When an overvoltage protection MOSFET is connected, DCLV is connected to DC when the input voltage is suitable for charging.                                   |

| 2   | DC   | Voltage-Sense Pin for DC Input from AC Adapter. Maximum operating voltage at this pin is 18V.                                                                                                                                                                                          |

| 3   | CHG  | CHG is an active-low, open-drain output that goes low when the MAX1874 is charging and goes high when both of the following conditions are met (see the <i>Battery Full (CHG)</i> section):  1) Charge current drops to a set threshold (Table 2).  2) The charger is in voltage mode. |

| 4   | USEL | USEL is a logic input that sets USB source charging current to 500mA when USEL is logic high and to 100mA when USEL is logic low.                                                                                                                                                      |

| 5   | EN   | Enable/Disable Input. Drive EN high to enable the device. When EN is low, $\overline{\text{UOK}}$ , $\overline{\text{DCOK}}$ , PON, and REF remain active.                                                                                                                             |

| 6   | GND  | Ground                                                                                                                                                                                                                                                                                 |

| 7   | DCI  | The voltage at this input sets the fast-charge current when the DCLV input is powering the charger. See the <i>Charging Current</i> section.                                                                                                                                           |

| 8   | THRM | THRM pauses charging when an externally connected thermistor ( $10k\Omega$ at +25°C) is at less than 0°C or greater than +50°C. Connect to GND to disable. See the <i>External Thermistor Monitor (THRM)</i> section.                                                                  |

| 9   | REF  | 3V Reference Output. Sources up to 500μA to bias I <sub>DCI</sub> and external thermistor. Bypass with 0.1μF to GND. REF loading does not affect BATT regulation accuracy.                                                                                                             |

| 10  | PGND | Power Ground. Connect to GND at a single, low-impedance point.                                                                                                                                                                                                                         |

| 11  | BYP  | BYP powers internal circuitry and switches to the active input (either DCLV or USB). Bypass with a 2.2µF capacitor to GND.                                                                                                                                                             |

| 12  | USB  | USB Charger Input. Charges BATT through an internal MOSFET.                                                                                                                                                                                                                            |

| 13  | ŪŌK  | UOK is an active-low, open-drain output that goes low to indicate when the USB input is the valid charging source.                                                                                                                                                                     |

| 14  | PON  | PON is an active-high, open-drain output with an internal $120k\Omega$ resistor to ground that goes high when $V_{DC}$ or $V_{USB} > V_{BATT}$ . PON can directly drive an external PFET that disconnects the battery from the system load when power is applied.                      |

| 15  | BATT | Charge Output. Connect to the positive terminal of the Li+ battery.                                                                                                                                                                                                                    |

| 16  | DCOK | DCOK is an active-low, open-drain output that goes low when 3.5V < V <sub>DC</sub> < 6.2V.                                                                                                                                                                                             |

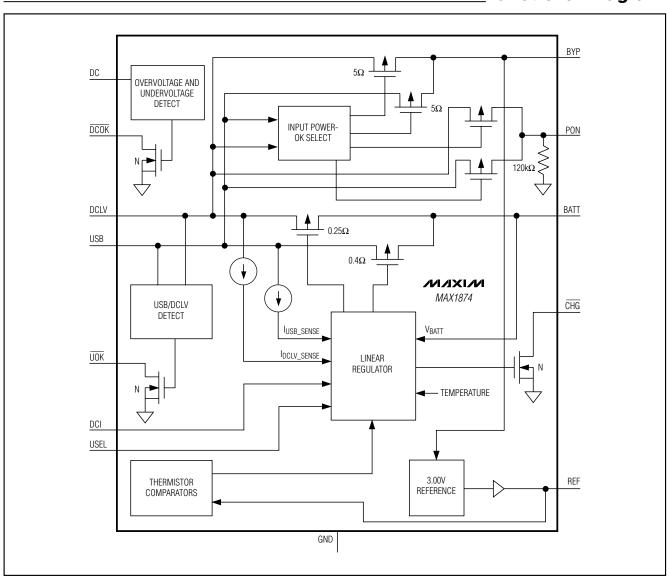

### **Functional Diagram**

#### **Detailed Description**

The MAX1874 charges a single-cell Li+ battery from either USB power sources or AC adapter sources. It contains a complete two-input linear charger that controls both battery charge current and voltage. In addition to all charging functions, the MAX1874 includes voltage-sensing and switchover circuitry that selects the active input source. When both inputs are active, priority is given to the AC adapter (DC). Charging current is regulated with on-chip power MOSFETs, so no external MOSFETs are required for a basic two-input charger. Additional features such as input-voltage protection and battery-load switching can be added with external MOSFETs that are driven directly from MAX1874 outputs.

The MAX1874 also features a thermal regulation loop that adjusts charging current so the die temperature remains below +105°C. See the *Package Thermal Limiting* section. This on-chip thermal control simplifies PC board layout and allows the optimum charging rate to be set without the thermal limits imposed by worst-case battery and input voltage. When the MAX1874 thermal limit is reached, the charger does not shut down but reduces charging current.

In addition to, and separate from, its internal die temperature control, the MAX1874 can also monitor ambient or cell temperature with an external thermistor connected to THRM. When the thermistor temperature is out of range (greater than +50°C or less than 0°C), charging stops until the temperature returns to normal. See the External Thermistor Monitor (THRM) section.

Other features include a  $\overline{\text{CHG}}$  output to indicate battery full (when charge current tapers to a percentage of fast-charge current).  $\overline{\text{DCOK}}$ ,  $\overline{\text{UOK}}$ , and power-on (PON) outputs indicate when valid power is present. These outputs can drive overvoltage protection and power selection MOSFETs (Figures 3, 4, and 5).

When charging is stopped or input power is removed, battery leakage is typically 5µA. No input blocking diodes are required to prevent battery drain.

With USB power connected, but without power at the DC input, charge current can be set to either 500mA or

100mA through the USEL input. When power is taken from the DC input, charge current is linearly set by the voltage at DCI. The MAX1874 charge current can also be DAC controlled with the output of a DAC connected to DCI. See the *Charging Current* section.

#### Enable (EN)

The enable input, EN, switches the MAX1874 on or off. With EN high, the MAX1874 is on and can begin charging. When EN is low, UOK, DCOK, PON, and REF remain active. Charging stops when EN is low, but the chip remains biased and continues to draw current from the input supplies so power-monitoring outputs can remain valid.

#### **USB-to-Adapter Power Handoff**

The MAX1874 can charge from either the USB input or the DC input. It cannot charge from both sources at the same time. The IC automatically selects the active input and charges from that. If both power sources are active, the adapter input (DC) takes precedence. Table 1 describes the switchover between DC and USB.

DC serves as the sense input for the adapter power source. This input senses when DC is above 6.2V (maximum range is 18V) or below 4V. When it senses the DC source is above 6.2V, DCOK goes high, indicating an invalid DC input. See the DC Power-OK (DCOK) section.

When power is connected to DC, the MAX1874 requires 20ms to validate the input. Consequently, charging is interrupted for 20ms until it is determined that input power is good. Also, when DC power is removed while valid USB power is present, charging is interrupted for 20ms before transferring to the USB source.

#### DC Power-OK (DCOK)

DCOK is an active-low, open-drain output that goes low when VDC is below 6.2V or above 3.5V. DCOK can be used as a logic output, but is also designed to drive an external MOSFET (Q2 in Figures 3, 4, and 5). This allows the charger to protect the input from overvoltage up to 18V. Charging is disabled for inputs over 6.2V. An external  $1k\Omega$  pullup resistor keeps  $\overline{DCOK}$  high (external MOSFET off) until it is certain the voltage is within the

Table 1. USB and DC Input Selection

| V <sub>DC</sub> > 18V OR V <sub>USB</sub> > 6.5V                                             | 4V < V <sub>DC</sub> < 6.2V AND<br>0 < V <sub>USB</sub> < 6.5V |    | $4V < V_{USB} < 6.5V \text{ AND}$<br>$V_{DC} < 4V \text{ OR } V_{DC} > 6.2V$                                                        | V <sub>DC</sub> < 4V OR V <sub>DC</sub> > 6.2V, AND V <sub>USB</sub> < 4V |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Exceeds operating input range. Not allowed. See the <i>Absolute Maximum Ratings</i> section. | DCLV powers device<br>and supplies charging<br>current.        | 1) | USB powers device and supplies charging current. DCLV disconnected from DC source through external MOSFET (Q2 Figures 3, 4, and 5). | No charging                                                               |

**Note:** V<sub>DC</sub> takes precedence when both inputs are valid.

acceptable range. To verify that the input voltage is stable,  $\overline{DCOK}$  has an internal delay of 20ms before connecting power to DCLV.  $\overline{DCOK}$  remains operational when EN is low (charger off).

#### **USB Power-OK (UOK)**

$\overline{\text{UOK}}$  is an active-low, open-drain output that goes low to indicate that V<sub>USB</sub> is valid (greater than 4V).  $\overline{\text{UOK}}$  remains operational when EN is low (charger off). An external 10k $\Omega$  pullup resistor keeps  $\overline{\text{UOK}}$  high until it is certain that power is within the acceptable range.  $\overline{\text{UOK}}$  can be used as a logic output, or to control a MOSFET that switches USB power directly to the system load when the MAX1874 is powered from a USB source (Q1 in Figure 4).

#### Bypass (BYP)

BYP is the bypass connection for the MAX1874's internal power rail. Bypass to GND with a 2.2 $\mu$ F or greater capacitor. The voltage at BYP is supplied from either DCLV or USB through an internal 5 $\Omega$  switch network.

#### Power On (PON)

PON goes high when V<sub>DC</sub> or V<sub>USB</sub> is within its normal operating range. PON can be used as a logic output to indicate power is connected or can drive an external P-channel MOSFET that switches the system load from the battery to an external source when power is applied. See Q3 in Figures 4 and 5.

## Charging Current Precharge Current

When the MAX1874 is powered with a battery connected, the IC first detects if the cell voltage is ready for full charge current. If the cell voltage is less than the prequal level (3V typ), the battery is precharged with a 50mA current until the cell reaches the proper level. The full charging current, as set by USEL or DCI, is then applied.

#### USEL

The charging current from the USB source is selected by USEL. A USB source can supply a maximum of 100mA or 500mA. USB hosts and powered hubs typically supply 500mA, while unpowered hubs supply 100mA. A logic low on USEL selects a 100mA maximum charging current. A logic high on USEL selects a 500mA maximum charging current.

#### DCI

When charging from the DCLV input, the voltage at DCI sets the charge current. The voltage-to-current transfer ratio from DCI to BATT is 1A/V<sub>REF</sub>. The DCI pin should be connected to a resistive divider from REF to DCI to GND (R5 and R6 in Figures 2 and 4). In this configuration, I<sub>BATT</sub> is as follows:

$$I_{BATT} = [R6 / (R5 + R6)] Amps$$

R5 and R6 should total 25k $\!\Omega$  or more to minimize loading on REF. Connecting DCI directly to REF results in a 1A charge current.

#### **Battery Full (CHG)**

CHG is low when the MAX1874 is charging in either the prequal or full-charging state. CHG then goes high when the charging current falls below a percentage of the set fast-charge current (Table 2) and the charger is in voltage mode (VBATT near 4.2V). The CHG current threshold is a function of the charger mode. When charging from a DC source, CHG goes high when IBATT falls to 12.5% of the current set by VDCI and the charger is in voltage mode (VBATT near 4.2V). When charging from a USB source with USEL high, CHG goes high when IBATT falls to 125mA and the charger is in voltage mode. If the MAX1874 is charging from a USB source with USEL low, CHG goes high when the charger enters voltage mode.

#### **Package Thermal Limiting**

On-chip thermal limiting in the MAX1874 simplifies PC board layout and allows charging rates to be automatically optimized without constraints imposed by worst-case minimum battery voltage, maximum input voltage, and maximum ambient temperature. When the MAX1874 thermal limit is reached, the charger does not shut down but simply reduces charging current. This allows the board design to be optimized for compact size and typical thermal conditions. The MAX1874 reduces charging current to keep its die temperature below +105°C.

### Table 2. CHG Battery Full Indication

| CHARGING SOURCE                | CHARGE CURRENT THRESHOLD FOR CHG GOING HIGH                    |

|--------------------------------|----------------------------------------------------------------|

| DCLV Charging                  | 12.5% of Charge Current Set by DCI and Charger in Voltage Mode |

| USB Charging 500mA (USEL high) | 125mA and Charger in Voltage Mode                              |

| USB Charging 100mA (USEL low)  | Charger in Voltage Mode                                        |

**Note:** CHG does not go high when charge current is reduced by the thermal regulation loop.

The MAX1874's thin QFN package includes a bottom metal plate that reduces thermal resistance between the die and the PC board. The external pad should be soldered to a large ground plane. This helps dissipate power and keeps the die temperature below the thermal limit. The MAX1874 thermal resistance from the die to the package thermal pad is typically 5°C/W. The thermal resistance of 1in<sup>2</sup> of 1oz copper on typical FR4 PC board material in free air is +42°C/W (typ). Consequently, the PC board pad area dominates the MAX1874's ability to dissipate heat. The MAX1874's thermal regulator is set for a +105°C die temperature. With the example thermal resistance of +47°C/W, the MAX1874 charge-current thermal limiting can be expected to occur when dissipating approximately 1.7W at +25°C ambient, and when dissipating approximately 0.75W at +70°C ambient.

The power dissipated in the charger is PDISS =  $[V_{IN}]$  (either VUSB or VDCLV) - VBATT] × ICHARGE. Power dissipation drops as the battery voltage rises, so thermal-charge current limiting, if it occurs, typically releases soon after charging begins and has little impact on charge time.

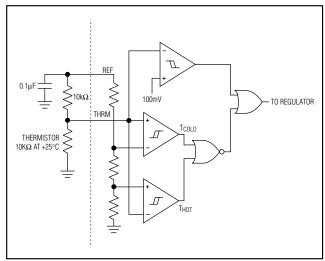

#### External Thermistor Monitor (THRM)

The MAX1874 features an internal window comparator to monitor battery pack temperature or ambient temperature with an external negative temperature coefficient thermistor. In typical systems, temperature is monitored to prevent charging at ambient temperature extremes (below 0°C or above +50°C). When the temperature moves outside these limits, charging is stopped. If the VTHERM returns to within its normal window, charging resumes. Connect THRM to GND when not using this feature. The THRM block diagram is detailed in Figure 1. Note that the temperature monitor at THRM is entirely separate from the on-chip temperature limiting discussed in the *Package Thermal Limiting* section.

The input thresholds for the THRM input are 0.74  $\times$  VREF for the COLD trip point and 0.29  $\times$  VREF for the HOT trip point.

### Applications Information

#### Input Overvoltage Protection Switch

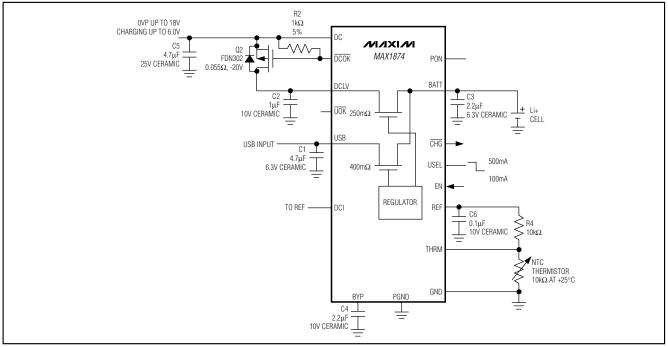

The DCLV input from an AC adapter or other source can be protected against overvoltage of up to 18V by connecting an external P-channel MOSFET (Q2 in Figures 3, 4, and 5) between DC and DCLV. When  $V_{DC}$  exceeds 6.2V, the  $\overline{DCOK}$  output turns the P-channel MOSFET off. On power-up,  $\overline{DCOK}$  remains high until it has been verified that  $V_{DC}$  is in range. If protection above 6.5V is not needed, then the MOSFET from the DC to DCLV can be omitted (Figure 2).

Figure 1. Thermistor Sensing Block Diagram

#### **Battery-Load Switch**

When input power is connected to the charger, some systems prefer that the battery is disconnected from the load and that system load current is taken directly from the DC input or USB source. This is an alternative to the basic case where the system load is permanently connected to the battery. The later setup is lower cost but has the disadvantage that if the battery is completely discharged, the system might not be ready to operate immediately, or might have limited functionality immediately upon plugging in the charger. If the battery has a load-disconnect switch, the system is more complex, but operation does not depend on the state of the battery. When system power is taken from the DC or USB input source, use D1, D2, Q1, and Q2 (Figure 4).

A partial approach to battery-load switching can connect the AC power adapter (DC) directly to the load, but not USB power (Figure 5). This can be useful when USB power is insufficient to fully power the system and charge the battery. When DC is powered, D2 provides a direct connection to the system and Q3 disconnects the battery. The battery does not power the load while it is charging. When only USB is connected, there is no bypass path from USB to the system. The battery is charged from the BATT output, and any system power is drawn from the battery through D5. If the system load exceeds the current supplied by the charger from USB (500mA or 100mA), then the battery can still discharge. In addition, if the system load does not allow the BATT current to fall below the USB battery full current threshold listed in Table 2, then CHG does not go high to indicate a full battery.

Figure 2. A Minimal Circuit that Assumes System Load Is Only Connected to the Battery. The circuit has a 6.5V maximum input and disables charging for inputs over 6.2V.

Figure 3. A circuit with overvoltage protection MOSFET (Q2) on DC input withstands up to 18V from the AC adapter and disables charging at inputs over 6.2V.

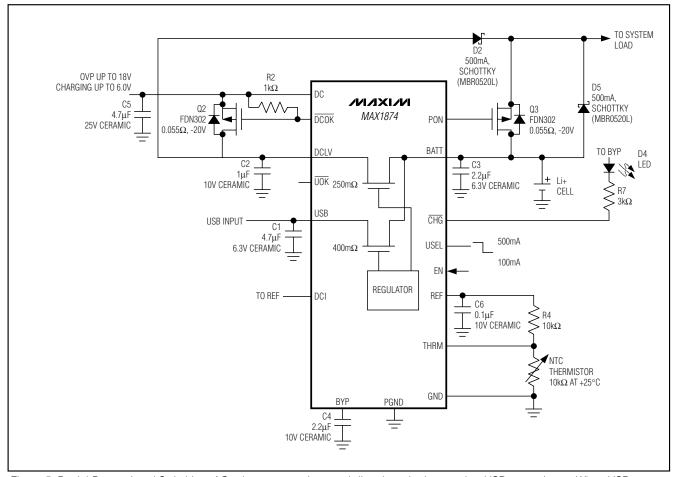

Figure 4. Full-Featured Circuit. Overvoltage protection MOSFET (Q2) on DC withstands up to 18V from the AC adapter, but disables charging at inputs over 6.2V. Output switch-over MOSFET (Q3) disconnects the battery from the system load when input power is applied. The input can power the system through D1, D2, Q1, and Q2 when either USB or AC power is present.

Figure 5. Partial-Battery Load Switching. AC adapter power is routed directly to the battery, but USB power is not. When USB power is connected, total USB current is limited to that set by USEL and system power is drawn from the battery through D5.

### Chip Information

TRANSISTOR COUNT: 4997

PROCESS: BICMOS

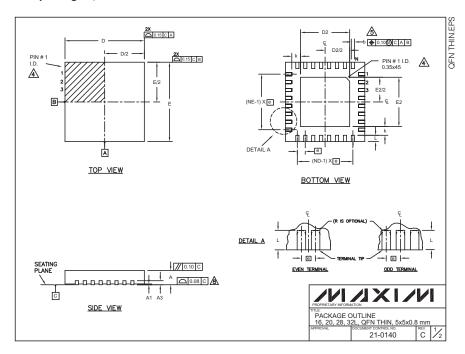

#### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|              |      |          |      | CC             | OMMC      | N DIME | NSIO      | NS       |         |           |          |     |

|--------------|------|----------|------|----------------|-----------|--------|-----------|----------|---------|-----------|----------|-----|

| PKG. 16L 5x5 |      |          |      | 20L 5x5        |           |        | 28L 5x5   | i        | 32L 5x5 |           |          |     |

| SYMBOL       | MIN. | NOM.     | MAX. | MIN. NOM. MAX. |           | MIN.   | NOM.      | MAX.     | MIN.    | NOM.      | MA       |     |

| Α            | 0.70 | 0.75     | 0.80 | 0.70           | 0.75      | 0.80   | 0.70      | 0.75     | 0.80    | 0.70      | 0.75     | 9.0 |

| A1           | 0    | 0.02     | 0.05 | 0              | 0.02      | 0.05   | 0         | 0.02     | 0.05    | 0         | 0.02     | 0.0 |

| A3           |      | 0.20 REF |      |                | 0.20 REF. |        |           | ).20 REI | F.      | - (       | 0.20 REF |     |

| b            | 0.25 | 0.30     | 0.35 | 0.25           | 0.30      | 0.35   | 0.20      | 0.25     | 0.30    | 0.20      | 0.25     | 0.3 |

| D            | 4.90 | 5.00     | 5.10 | 4.90           | 5.00      | 5.10   | 4.90      | 5.00     | 5.10    | 4.90      | 5.00     | 5.1 |

| Е            | 4.90 | 5.00     | 5.10 | 4.90           | 5.00      | 5.10   | 4.90      | 5.00     | 5.10    | 4.90      | 5.00     | 5.1 |

| •            |      | 0.80 BS  | C.   | 0.65 BSC.      |           |        | 0.50 BSC. |          |         | 0.50 BSC. |          |     |

| k            | 0.25 | -        | -    | 0.25           | -         | -      | 0.25      | -        |         | 0.25      | -        |     |

| L            | 0.45 | 0.55     | 0.65 | 0.45           | 0.55      | 0.65   | 0.45      | 0.55     | 0.65    | 0.30      | 0.40     | 0.8 |

| N            | 16   |          |      |                | 20        |        |           | 28       | •       |           | 32       |     |

| ND           |      | 4        |      | 5              |           |        |           | 7        |         |           | 8        |     |

| NE           |      | 4        |      | 5              |           |        | 7         |          |         | 8         |          |     |

| JEDEC        |      | WHHB     |      |                | WHHC      |        |           | WHHD-    | -1      |           | WHHD     | -2  |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |

|------------------------|------|------|------|------|------|------|

| PKG.                   | D2   |      |      | E2   |      |      |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |

| T1655-1                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |

| T2055-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |

| T2855-1                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |

| T2855-2                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |

| T3255-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994

- 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

2. NLS THE TOTAL NUMBER OF TERMINALS.

AN IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ANE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE NDIOCATED. THE TERMINAL #1 IDENTIFIER MAY BE BETHER A MOLD OR MARKED FEATURE.

⚠ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm

♠ NO AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

⚠ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220 10. WARPAGE SHALL NOT EXCEED 0.10 mm

т.е: PACKAGE OUTLINE 16, 20, 28, 32L, QFN THIN, 5x5x0.8 mn C 2/2 21-0140

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600