## **General Description**

The MAX5360/MAX5361/MAX5362 are low-cost, 6-bit digital-to-analog converters (DACs) in miniature 5-pin SOT23 packages with a simple 2-wire serial interface that allows communication with multiple devices. The MAX5360 has an internal +2V reference and operates from a +2.7V to +3.6V supply. The MAX5361 has an internal +4V reference and operates from a +4.5V to +5.5V supply. The MAX5362 operates over the full +2.7V to +5.5V supply range and has an internal reference equal to  $0.9 \times V_{DD}$ .

The fast-mode I<sup>2</sup>C<sup>™</sup>-compatible serial interface allows communication at data rates up to 400kbps, minimizing board space and reducing interconnect complexity in many applications. Each device is available with one of four factory-preset addresses (see Selector Guide).

The MAX5360/MAX5361/MAX5362 also include an output buffer, a low-power shutdown mode, and a poweron reset that ensures the DAC outputs are at zero when power is initially applied. In shutdown mode, the supply current is reduced to less than 1µA and the output is pulled down with a  $10k\Omega$  resistor to GND.

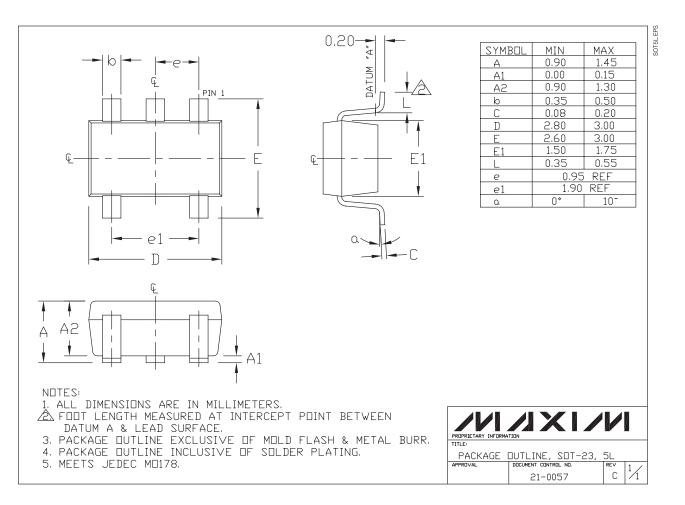

The MAX5360/MAX5361/MAX5362 are available in miniature 5-pin SOT23 packages.

## **Applications**

Automatic Tuning (VCO) Power Amplifier Bias Control Programmable Threshold Levels Automatic Gain Control Automatic Offset Adjustment

I<sup>2</sup>C is a trademark of Philips Corp.

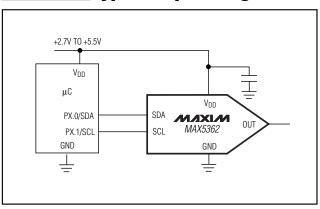

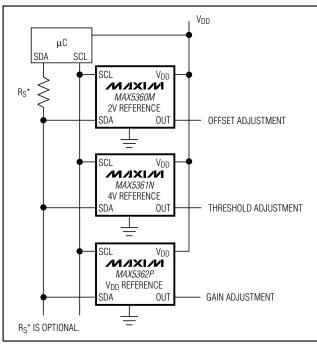

## Typical Operating Circuit

#### Features

- ♦ 6-Bit Accuracy in a Tiny 5-Pin SOT23 Package

- ♦ Wide +2.7V to +5.5V Supply Range (MAX5362)

- ♦ 1µA Shutdown Mode

- **♦** Buffered Output Drives Resistive Loads

- ♦ Low Glitch Power-On-Reset to Zero DAC Output

- ♦ Fast I<sup>2</sup>C-Compatible Serial Interface

- ♦ ≤-5% Full-Scale Error (MAX5362)

- ♦ ≤1LSB (max) INL/DNL

- ♦ Low 230µA max Supply Current

## **Ordering Information**

| PART           | TEMP. RANGE    | PIN-PACKAGE |

|----------------|----------------|-------------|

| MAX5360_EUK-T* | -40°C to +85°C | 5 SOT23-5   |

| MAX5361_EUK-T* | -40°C to +85°C | 5 SOT23-5   |

| MAX5362_EUK-T* | -40°C to +85°C | 5 SOT23-5   |

<sup>\*</sup>See Selector Guide for address options.

## Selector Guide

| PART        | ADDRESS | REFERENCE           | TOP<br>MARK |

|-------------|---------|---------------------|-------------|

| MAX5360LEUK | 0x60    | +2.0V               | ADMM        |

| MAX5360MEUK | 0x62    | +2.0V               | ADMY        |

| MAX5360NEUK | 0x64    | +2.0V               | ADNE        |

| MAX5360PEUK | 0x66    | +2.0V               | ADMO        |

| MAX5361LEUK | 0x60    | +4.0V               | ADMU        |

| MAX5361MEUK | 0x62    | +4.0V               | ADNA        |

| MAX5361NEUK | 0x64    | +4.0V               | ADNG        |

| MAX5361PEUK | 0x66    | +4.0V               | ADMQ        |

| MAX5362LEUK | 0x60    | $0.9 \times V_{DD}$ | ADMW        |

| MAX5362MEUK | 0x62    | $0.9 \times V_{DD}$ | ADNC        |

| MAX5362NEUK | 0x64    | $0.9 \times V_{DD}$ | ADNI        |

| MAX5362PEUK | 0x66    | $0.9 \times V_{DD}$ | ADMS        |

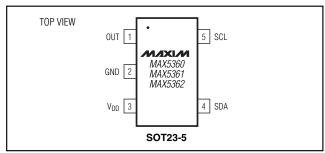

# Pin Configuration

MIXIM

Maxim Integrated Products 1

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +                       | 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571mW |

|-------------------------------------------------------|------------------------------------------------|

| OUT to GND0.3V to (V <sub>DD</sub> + 0.0              | V) Operating Temperature Range                 |

| SCL, SDA to GND0.3V to +                              | MAX536EUK-T40°C to +85°C                       |

| Maximum Current into Any Pin50                        | nA Storage Temperature Range65°C to +150°C     |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Maximum Junction Temperature+150°C             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 2.7V \text{ to } 3.6V \text{ (MAX5360)}; V_{DD} = 4.5V \text{ to } 5.5V \text{ (MAX5361)}; V_{DD} = 2.7V \text{ to } 5.5V \text{ (MAX5362)}; R_L = 10k\Omega, C_L = 50pF, T_A = T_{MIN} \text{ to } 1.5V \text{ (MAX5362)}; R_L = 10k\Omega, C_L = 50pF, T_A = T_{MIN} \text{ to } 1.5V \text{ (MAX5361)}; R_L = 10k\Omega, C_L = 50pF, T_A = T_{MIN} \text{ to } 1.5V \text{ (MAX5361)}; R_L = 10k\Omega, C_L = 50pF, T_A = T_{MIN} \text{ to } 1.5V \text{ (MAX5361)}; R_L = 10k\Omega, R_L = 10k$  $T_{MAX}$ , unless otherwise noted. Typical values are  $T_A = +25$ °C.)

| PARAMETER                         | SYMBOL | CONDITIONS                                             |                    | MIN             | TYP      | MAX      | UNITS      |  |

|-----------------------------------|--------|--------------------------------------------------------|--------------------|-----------------|----------|----------|------------|--|

| STATIC ACCURACY                   |        |                                                        |                    |                 |          |          |            |  |

| Resolution                        |        |                                                        |                    | 6               |          |          | Bits       |  |

| Integral Linearity Error          | INL    | (Note 1)                                               |                    |                 |          | ±1       | LSB        |  |

| Differential Linearity Error      | DNL    | Guaranteed monoton                                     | nic (Note 2)       |                 |          | ±1       | LSB        |  |

| Offset Error                      | Vos    | Guaranteed monoton                                     | nic (Note 2)       |                 | ±1       | ±2       | mV         |  |

| Offset Error Supply Rejection     |        | MAX5362 (Notes 2, 3                                    | 3)                 | 60              |          |          | dB         |  |

| Offset Error Temperature          |        | (Note 2)                                               | MAX5360/MAX5361    |                 | 3        |          | nnm/0C     |  |

| Coefficient                       |        | (Note 2)                                               | MAX5362            |                 | 1        |          | ppm/°C     |  |

| Full-Scale Error                  |        | Code = 63                                              | MAX5360/MAX5361    |                 |          | 10       | % of Ideal |  |

| Full-Scale Error                  |        | Code = 63                                              | MAX5362            |                 |          | 5        | FS         |  |

| Full-Scale Error Supply Rejection |        | Code = 63, MAX5360                                     | D/MAX5361 (Note 4) |                 |          | 60       | dB         |  |

| Full-Scale Error Temperature      |        | Code = 63                                              | MAX5360/MAX5361    |                 | ±40      |          | 10.00.000  |  |

| Coefficient                       |        | Code = 63                                              | MAX5362            |                 | ±10      |          | ppm/°C     |  |

| DAC OUTPUT                        |        |                                                        |                    |                 |          |          | •          |  |

|                                   |        | MAX5360                                                |                    | 1.8             | 2        | 2.2      |            |  |

| latamal Dafamana (Niata 5)        | DEE    | MAX5361                                                |                    | 3.6             | 4        | 4.4      | V          |  |

| Internal Reference (Note 5)       | REF    | MANGOOO                                                |                    | 0.85×           | 0.9×     | 0.95×    | \ \ \      |  |

|                                   |        | MAX5362                                                |                    | V <sub>DD</sub> | $V_{DD}$ | $V_{DD}$ |            |  |

| Output Load Regulation            |        | Code = 63, 0 to 100µA                                  |                    |                 | 0.5      |          | LSB        |  |

| Output Load negulation            |        | Code = 0, 0 to -100µ                                   |                    |                 | 0.5      |          | LSB        |  |

| Output Resistance                 |        | $V_{OUT} = 0$ to $V_{DD}$ , pov                        | wer-down mode      |                 | 10       |          | kΩ         |  |

| DYNAMIC PERFORMANCE               |        |                                                        |                    |                 |          |          |            |  |

| Voltage Output Slew Rate          |        | Positive and negative                                  |                    |                 | 0.4      |          | V/µs       |  |

| Output Settling Time              |        | To 1/2LSB, $50k\Omega$ and $50pF$ load (Note 6)        |                    | 20              |          | μs       |            |  |

| Digital Feedthrough               |        | Code = 0, all digital inputs from 0 to V <sub>DD</sub> |                    |                 | 2        |          | nVs        |  |

| Digital-Analog Glitch Impulse     |        | Code 31 to 32                                          |                    |                 | 40       |          | nVs        |  |

| Wake-Up Time                      |        | From software shutdo                                   | own                |                 | 50       |          | μs         |  |

MIXIM

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX5360);\ V_{DD}=4.5V\ to\ 5.5V\ (MAX5361);\ V_{DD}=2.7V\ to\ 5.5V\ (MAX5362);\ R_L=10k\Omega,\ C_L=50pF,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are  $T_A=+25^{\circ}C.)$

| PARAMETER                        | SYMBOL           | COND                                                           | ITIONS                                 | MIN                 | TYP                  | MAX                | UNITS |  |

|----------------------------------|------------------|----------------------------------------------------------------|----------------------------------------|---------------------|----------------------|--------------------|-------|--|

| POWER REQUIREMENTS               |                  |                                                                |                                        |                     |                      |                    |       |  |

|                                  |                  | MAX5360                                                        |                                        | 2.7                 |                      | 3.6                |       |  |

| Supply Voltage                   | V <sub>DD</sub>  | MAX5361                                                        |                                        | 4.5                 |                      | 5.5                | V     |  |

|                                  |                  | MAX5362                                                        |                                        | 2.7                 |                      | 5.5                |       |  |

| Supply Current                   | loo              | No load, all digital input                                     | ts at 0 or V <sub>DD</sub> , code = 63 |                     | 150                  | 230                | ^     |  |

| Supply Current                   | IDD              | Shutdown mode                                                  |                                        |                     |                      | 1                  | μΑ    |  |

| <b>DIGITAL INPUTS</b> (SCL, SDA) |                  |                                                                |                                        |                     |                      | •                  |       |  |

| Input Low Voltage                | VIL              |                                                                |                                        |                     | 0.                   | $.3 \times V_{DD}$ | V     |  |

| Input High Voltage               | VIH              |                                                                |                                        | $0.7 \times V_{DD}$ |                      |                    | V     |  |

| Input Hysteresis                 | V <sub>hys</sub> |                                                                |                                        | 0.0                 | 05 × V <sub>DI</sub> | D                  | V     |  |

| Input Capacitance                | CIN              | (Note 7)                                                       |                                        |                     | 10                   |                    | рF    |  |

| Input Leakage Current            | li               |                                                                |                                        |                     |                      | ±10                | μΑ    |  |

| Pulse Width of Spike Suppressed  | tsp              |                                                                |                                        | 0                   |                      | 50                 | ns    |  |

| DIGITAL OUTPUT (SDA) (open       | drain)           |                                                                |                                        |                     |                      |                    |       |  |

| Output Low Voltage               | VoL              | I <sub>SINK</sub> = 3mA                                        |                                        |                     | 0                    | 0.4                | V     |  |

| Output Low Voltage               | VOL              | ISINK = 6mA                                                    |                                        |                     | 0                    | 0.6                | V     |  |

| Output Fall Time                 | t <sub>of</sub>  | V <sub>IH</sub> min to V <sub>IL</sub> max,<br>bus capacitance | Isink = 3mA                            |                     |                      | 250                | ns    |  |

| Catpati an inno                  | -01              | 10pF to 400pF                                                  | Isink = 6mA                            |                     |                      | 250                | 110   |  |

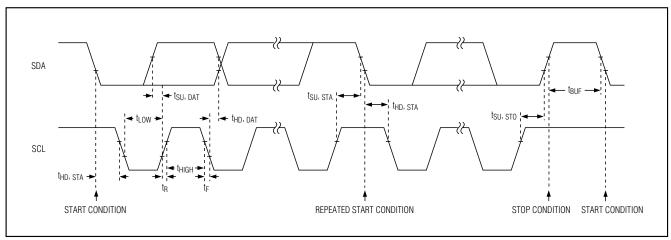

#### TIMING CHARACTERISTICS

$(V_{DD}=2.7V \text{ to } 3.6V \text{ (MAX5360)}; V_{DD}=4.5V \text{ to } 5.5V \text{ (MAX5361)}; V_{DD}=2.7V \text{ to } 5.5V \text{ (MAX5362)}; R_L=10k\Omega, C_L=50pF, T_A=T_{MAX} \text{ to } T_{MIN}, Figure 3, unless otherwise noted. Typical values are T_A=+25°C.)$

| PARAMETER                                          | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|------------------|------------|-----|-----|-----|-------|

| SCL Clock Frequency                                | f <sub>SCL</sub> |            | 0   |     | 400 | kHz   |

| Bus-Free Time Between a STOP and a START Condition | t <sub>BUF</sub> |            | 1.3 |     |     | μs    |

| Hold Time (Repeated)<br>START Condition            | thd, sta         |            | 0.6 |     |     | μs    |

| Low Period of the SCL Clock                        | tLOW             |            | 1.3 |     |     | μs    |

| High Period of the SCL Clock                       | thigh            |            | 0.6 |     |     | μs    |

## **TIMING CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX5360);\ V_{DD}=4.5V\ to\ 5.5V\ (MAX5361);\ V_{DD}=2.7V\ to\ 5.5V\ (MAX5362);\ R_L=10k\Omega,\ C_L=50pF,\ T_A=T_{MAX}\ to\ T_{MIN},\ Figure\ 3,\ unless\ otherwise\ noted.$  Typical values are  $T_A=+25^{\circ}C.)$

| PARAMETER                                 | SYMBOL               | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------------|----------------------|------------|-----|-----|-----|-------|

| Setup Time for a Repeated START Condition | t <sub>SU, STA</sub> |            | 0.6 |     |     | μs    |

| Data Hold Time                            | thd, dat             |            | 0   |     | 0.9 | μs    |

| Data Setup Time                           | tsu, dat             |            | 100 |     |     | ns    |

| Rise Time of Both SDA and SCL Signals     | t <sub>r</sub>       |            |     |     | 300 | ns    |

| Fall Time of Both SDA and SCL Signals     | t <sub>f</sub>       |            |     |     | 300 | ns    |

| Setup Time for STOP Condition             | tsu, sto             |            | 0.6 |     |     | μs    |

| Capacitive Load for Each<br>Bus Line      | Cb                   |            |     |     | 400 | pF    |

Note 1: Guaranteed from code 1 to code 63.

Note 2: The offset value extrapolated from the range over which the INL is guaranteed.

**Note 3:** MAX5362, tested at  $V_{DD} = 5V \pm 10\%$ .

Note 4: MAX5360, tested at  $V_{DD}$  = 3V ±10%; MAX5361, tested at  $V_{DD}$  = 5V ±10%.

Note 5: Actual output voltage at full scale is 63/64 × V<sub>REF</sub>.

Note 6: Output settling time is measured by taking the code from code 1 to code 63, and from code 63 to code 1.

Note 7: Guaranteed by design.

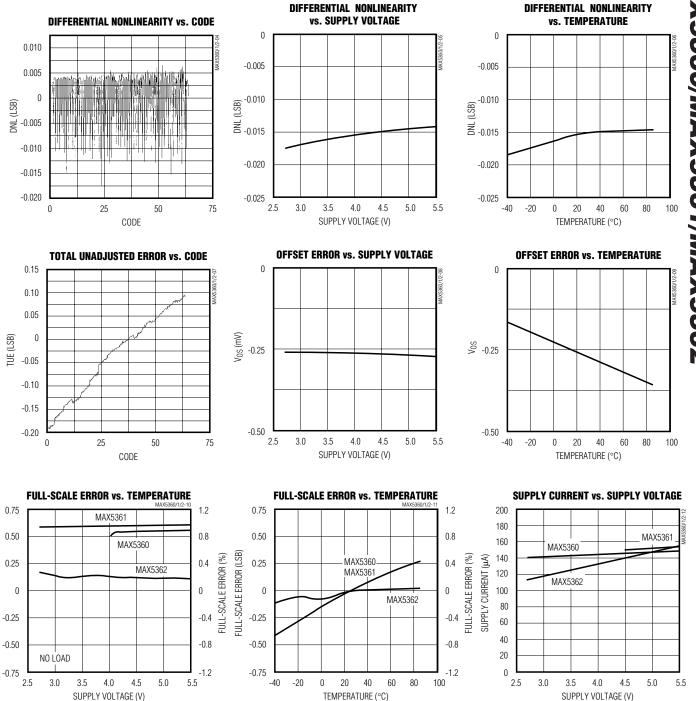

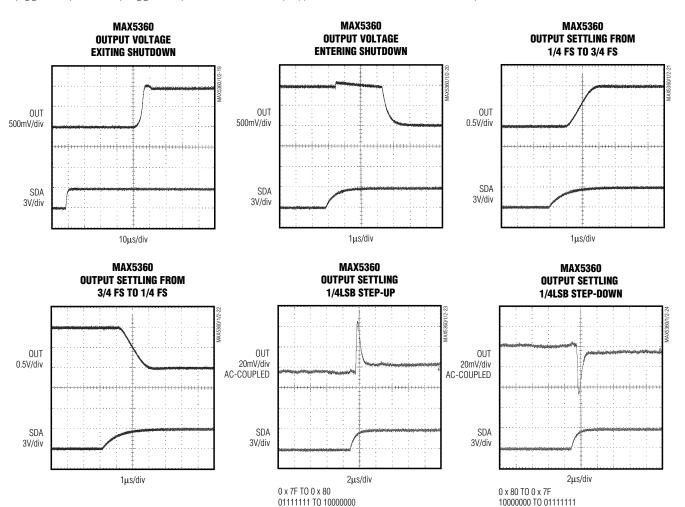

# \_Typical Operating Characteristics

$(V_{DD} = 3V (MAX5360), V_{DD} = 5V (MAX5361/MAX5362), T_A = +25$ °C, unless otherwise noted.)

# MAX5360/MAX5361/MAX5362

# Low-Cost, Low-Power 6-Bit DACs with 2-Wire Serial Interface in SOT23 Package

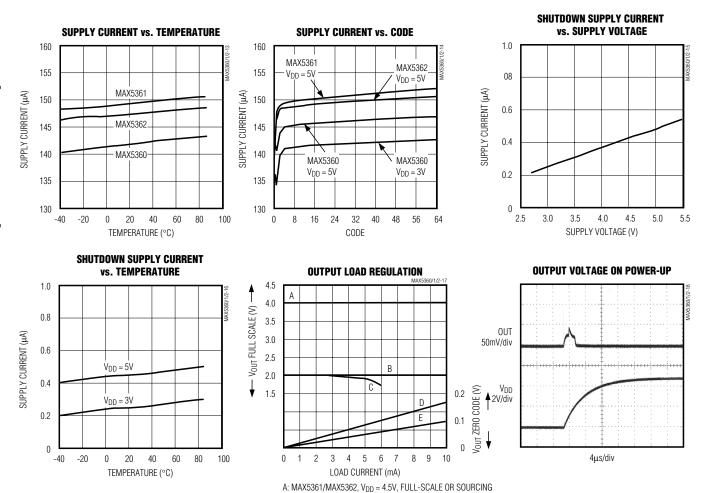

## **Typical Operating Characteristics (continued)**

$(V_{DD} = 3V \text{ (MAX5360)}, V_{DD} = 5V \text{ (MAX5361/MAX5362)}, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

FULL-SCALE ERROR (LSB)

## Typical Operating Characteristics (continued)

$(V_{DD} = 3V \text{ (MAX5360)}, V_{DD} = 5V \text{ (MAX5361/MAX5362)}, T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{DD} = 3V \text{ (MAX5360)}, V_{DD} = 5V \text{ (MAX5361/MAX5362)}, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

## **Pin Description**

| PIN | NAME            | FUNCTION           |

|-----|-----------------|--------------------|

| 1   | OUT             | DAC Voltage Output |

| 2   | GND             | Ground             |

| 3   | V <sub>DD</sub> | Power-Supply Input |

| 4   | SDA             | Serial Data Input  |

| 5   | SCL             | Serial Clock Input |

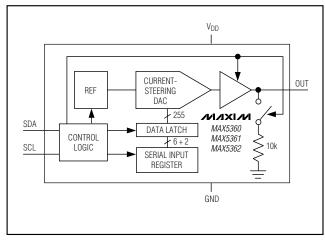

Figure 1. Functional Diagram

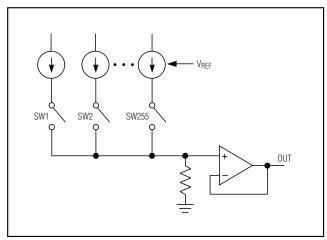

Figure 2. Current-Steering Topology

## **Table 1. Unipolar Code Current**

| DAC CODE           | OUTPUT VOLTAGE |              |                                 |  |  |  |

|--------------------|----------------|--------------|---------------------------------|--|--|--|

| 6 BITS + 2 SUBBITS | MAX5360        | MAX5361      | MAX5362                         |  |  |  |

| 111111 (00)        | 2V × (63/64)   | 4V × (63/64) | 0.9 × V <sub>DD</sub> × (63/64) |  |  |  |

| 100000 (00)        | 1V             | 2V           | 0.9 × V <sub>DD</sub> / 2       |  |  |  |

| 000001 (00)        | 31mV           | 62mV         | 0.9 × V <sub>DD</sub> / 64      |  |  |  |

| 000000 (00)        | 0              | 0            | 0                               |  |  |  |

## **Detailed Description**

The MAX5360/MAX5361/MAX5362 voltage-output, 6-bit DACs offer full 6-bit performance with less than 1LSB integral nonlinearity (INL) error and less than 1LSB differential nonlinearity (DNL) error ensuring monotonic performance. The devices use a simple two-wire, fast-mode I<sup>2</sup>C-compatible serial interface that operates up to 400kHz. The MAX5360/MAX5361/MAX5362 include an internal reference, an output buffer, and low-current shutdown mode, making them ideal for low-power, highly integrated applications. Figure 1 shows the devices' functional diagram.

#### **Analog Section**

The MAX5360/MAX5361/MAX5362 employ a currentsteering DAC topology as shown in Figure 2. At the core of the DAC is a reference voltage-to-current converter (V/I) that generates a reference current. This current is mirrored to 255 equally weighted current sources. DAC switches control the outputs of these current mirrors, so only the desired fraction of the total current-mirror currents is steered to the DAC output. The current is then converted to a voltage across a resistor, and this voltage is buffered by the output buffer amplifier.

#### Output Voltage

Table 1 shows the relationship between the DAC code and the analog output voltage. The 6-bit DAC code is binary unipolar with 1LSB = ( $V_{REF}$  / 64). The MAX5360/MAX5361 have a full-scale output voltage of (+2V - 1LSB) and (+4V - 1LSB), respectively, set by the internal references. The MAX5362 has a full-scale output voltage of (0.9 ×  $V_{DD}$  - 1LSB). Each device accepts 8-bit DAC codes, but the accuracy is guaranteed only for 6 bits.

## **Output Buffer**

The DAC voltage output is an internally buffered unity-gain follower that typically slews at  $\pm 0.4 \text{V}/\mu\text{s}$ . The output can swing from 0 to full scale. With a 1/4 FS to 3/4 FS output transition, the amplifier outputs typically settle to 1/2LSB in less than 5µs when loaded with 10k $\Omega$  in parallel with 50pF. The buffer amplifiers are stable with any combination of resistive loads >10k $\Omega$  and capacitive loads <50pF.

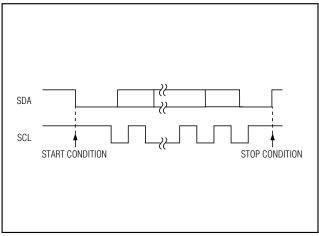

Figure 3. Two-Wire Serial Interface Timing Diagram

Figure 4. Typical Application Circuit

#### Power-On Reset

The MAX5360/MAX5361/MAX5362 have a power-on reset circuit to set the DAC's output to 0 when VDD is first applied or when VDD dips below 1.7V. This ensures that unwanted DAC output voltages will not occur immediately following a system startup, such as after a loss of power. The output glitch on startup is typically <50mV.

#### Shutdown Mode

The MAX5360/MAX5361/MAX5362 include a software-controlled shutdown mode that reduces the supply current to <1 $\mu$ A. All internal circuitry is disabled and an internal 10k $\Omega$  resistor is placed from OUT to GND to ensure 0V at OUT while in shutdown. The device enters shutdown in less than 5 $\mu$ s and exits shutdown in less than 50 $\mu$ s.

## **Digital Section**

#### Serial interface

The MAX5360/MAX5361/MAX5362 use a simple two-wire serial interface requiring only two I/O lines (two-wire bus) of a standard microprocessor ( $\mu$ P) port. Figure 3 shows the timing diagram for signals on the 2-wire bus.

The two bus lines (SDA and SCL) must be high when the bus is not in use. The MAX5360/MAX5361/ MAX5362 are receive-only devices (slaves) and must be controlled by a bus master device. Figure 4 shows a typical application where multiple devices can be connected to the bus provided they have different address settings. External pullup resistors are not necessary on these lines (when driven by push-pull drivers), though the MAX5360/MAX5361/MAX5362 can be used in applications where pullup resistors are required (such as in I<sup>2</sup>C systems) to maintain compatibility with existing circuitry. The serial interface operates at SCL rates up to 400kHz. The SDA state is allowed to change only while SCL is low, with the exception of START and STOP conditions as shown in Figure 5. Each transmission consists of a START condition sent by the bus master device, followed by the MAX5360/MAX5361/ MAX5362's preset slave address, a power-mode bit,

Figure 5. Start and Stop Conditions

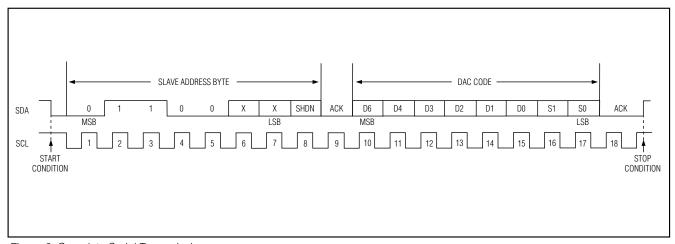

the DAC data (6 bits + 2 subbits), and finally, a STOP condition (Figure 6). The bus is then free for another transmission.

SDA's state is sampled, and therefore must remain stable while SCL is high. Data is transmitted in 8-bit bytes. Nine clock cycles are required to transfer each byte to the MAX5360/MAX5361/MAX5362. Release SDA during the 9th clock cycle as the selected device acknowledges the receipt of the byte, by pulling SDA low during this time. A series resistor on the SDA line may be needed if the master's output is forced high while the selected device acknowledges (Figure 4).

#### Slave Address

The MAX5360/MAX5361/MAX5362 are available with one of four preset slave addresses. Each address option is identified by the suffix L, M, N, or P added to the part number. The address is defined as the 7 most significant bits (MSBs) sent by the master after a START condition. The address options are 0x60, 0x62, 0x64, and 0x66 (left justified with LSB set to 0). The 8th bit, typically used to define a write or read protocol, sets the device's power mode (SHDN); the device is powered down when SHDN is set to 1. During a device search routine, the MAX5360/MAX5361/MAX5362 acknowledge both options (SHDN = 0 or SHDN = 1) but does not change its power state if a stop condition (or restart) is issued immediately. The second byte (DAC data) must be sent/received for the device to update both power mode and DAC output.

#### DAC Data

The 6-bit DAC data is decoded as straight binary MSB first with 1LSB = (VREF / 64) and converted into the corresponding analog voltage as shown in Table 1. Two subbits complete the data byte; these 2 bits should be set to zero since they are not tested to guaranteed-monotonic performance.

After receiving the data byte, the MAX5360/MAX5361/MAX5362 acknowledge its receipt and expect a STOP condition, at which point the DAC output is updated. The devices update the output and the power mode only if the second byte is clocked in (SHDN = 0) or out (SHDN = 1) of the device. When SHDN = 1, the master will read all ones when clocking out a data byte. The MAX5360/MAX5361/MAX5362 do not drive SDA except for the acknowledge bit.

Figure 6. Complete Serial Transmission

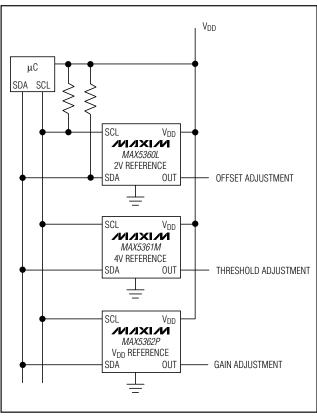

Figure 7. I<sup>2</sup>C Typical Application

#### I<sup>2</sup>C Compatibility

The MAX5360/MAX5361/MAX5362 are compatible with existing I<sup>2</sup>C systems. SCL and SDA are high-impedance inputs; SDA has an open drain that pulls the data line low during the 9th clock pulse. Figure 7 shows a

typical I<sup>2</sup>C application. The communication protocol supports the standard I<sup>2</sup>C 8-bit communications. The general call address is ignored, and CBUS formats are not supported. The MAX5360/MAX5361/MAX5362 address is compatible with the 7-bit I<sup>2</sup>C addressing protocol only. No 10-bit formats are supported. RESTART protocol is supported, but an immediate STOP condition is necessary to update the DAC.

## Applications Information

## **Digital Inputs and Interface Logic**

The serial 2-wire interface has logic levels defined as  $V_{OL} = 0.3 \times V_{DD}$  and  $V_{OH} = 0.7 \times V_{DD}$ . All of the inputs include Schmitt-trigger buffers to accept slow-transition interfaces. This means that optocouplers can interface directly to the MAX5360/MAX5361/MAX5362 without additional external logic. The digital inputs are compatible with CMOS logic levels and must not be driven with voltages higher than  $V_{DD}$ .

## **Power-Supply Bypassing and Layout**

Careful PC board layout is important for best system performance. To reduce crosstalk and noise injection, keep analog and digital signals separate. Ensure that the ground return from GND to the supply ground is short and low impedance; a ground plane is recommended. Bypass VDD with a 0.1 $\mu$ F to ground as close as possible to the device. If the supply is excessively noisy, connect a 10 $\Omega$  resistor in series with the supply and VDD, and add additional capacitance

# **Chip Information**

TRANSISTOR COUNT: 2910

PROCESS: BICMOS

## **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.