## Features

- High-performance, Low-power AVR<sup>®</sup> 8-bit Microcontroller

- Advanced RISC Architecture

- 133 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers + Peripheral Control Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- Nonvolatile Program and Data Memories

- 128K Bytes of In-System Reprogrammable Flash Endurance: 1,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- 4K Bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 4K Bytes Internal SRAM

- Up to 64K Bytes Optional External Memory Space

- Programming Lock for Software Security

- SPI Interface for In-System Programming

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode and Capture Mode

- Real Time Counter with Separate Oscillator

- Two 8-bit PWM Channels

- 6 PWM Channels with Programmable Resolution from 1 to 16 Bits

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

- 7 Differential Channels

- 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

- Byte-oriented 2-wire Serial Interface

- Dual Programmable Serial USARTs

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

- Software Selectable Clock Frequency

- ATmega103 Compatibility Mode Selected by a Fuse

- Global Pull-up Disable

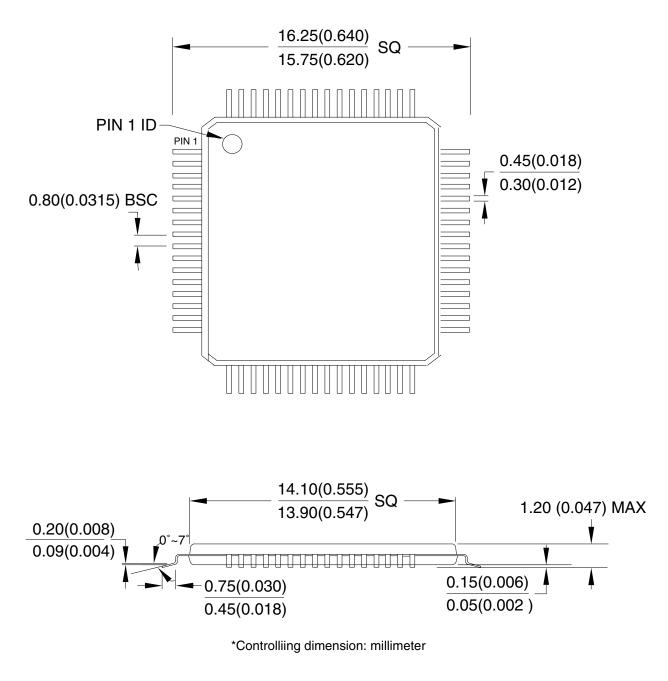

- I/O and Packages

- 53 Programmable I/O Lines

- 64-lead TQFP

- Operating Voltages

- 2.7 5.5V for ATmega128L

- 4.5 5.5V for ATmega128

- Speed Grades

- 0 8 MHz for ATmega128L

- 0 16 MHz for ATmega128

8-bit **AVR**<sup>®</sup> Microcontroller with 128K Bytes In-System Programmable Flash

ATmega128 ATmega128L

# Preliminary

Summary

Rev. 2467BS-09/01

Note: This is a summary document. A complete document is available on our web site at *www.atmel.com*.

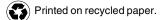

## **Pin Configurations**

Figure 1. Pinout ATmega128

## Overview

The ATmega128 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega128 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

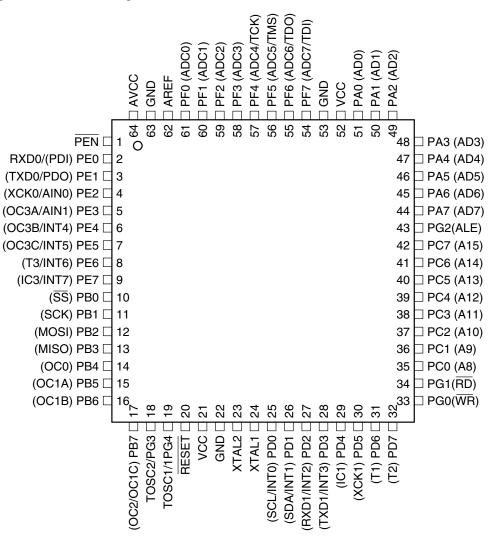

## **Block Diagram**

Figure 2. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega128 provides the following features: 128K bytes of In-System Programmable Flash with Read-While-Write capabilities, 4K bytes EEPROM, 4K bytes SRAM, 53 general-purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), four flexible timer/counters with compare modes and PWM, 2 USARTs, a byte oriented 2-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with internal oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, timer/counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction Mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main oscillator and the asynchronous timer continue to run.

The device is manufactured using Atmel's high-density nonvolatile memory technology. The on-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an on-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega128 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega128 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

The ATmega128 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O location reserved in the AVR instruction set. To ensure backward compatibility with the ATmega103, all I/O locations present in ATmega103 have the same location in ATmega128. Most additional I/O locations are added in an Extended I/O space starting from \$60 to \$FF, (i.e., in the ATmega103 internal RAM space). These location can be reached by using LD/LDS/LDD and ST/STS/STD instruction only, not by using IN and OUT instruction. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the increased number of interrupt vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega103 compatibility mode can be selected by programming the fuse M103C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega103. Also, the extended interrupt vectors are removed.

### ATmega103 and ATmega128 Compatibility

# ATmega128(L)

|                                 | The ATmega128 is 100% pin compatible with ATmega103, and can replace the ATmega103 on current Printed Circuit Boards. The application note "Replacing ATmega103 by ATmega128" describes what the user should be aware of replacing the ATmega103 by an ATmega128.                                                                                                                                                                         |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATmega103 Compatibility<br>Mode | By programming the M103C fuse, the ATmega128 will be compatible with the ATmega103 regards to RAM, I/O pins and interrupt vectors as described above. How-<br>ever, some new features in ATmega128 are not available in this compatibility mode, these features are listed below:                                                                                                                                                         |

|                                 | <ul> <li>One USART instead of two, asynchronous mode only. Only the 8 least significant<br/>bits of the Baud Rate Register is available.</li> </ul>                                                                                                                                                                                                                                                                                       |

|                                 | <ul> <li>One 16 bits Timer/Counter with 2 compare registers instead of two 16-bit<br/>Timer/Counters with 3 compare registers.</li> </ul>                                                                                                                                                                                                                                                                                                 |

|                                 | 2-wire serial interface is not supported.                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                 | <ul> <li>Port G serves alternate functions only (not a general I/O port).</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

|                                 | <ul> <li>Port F serves as digital input only in addition to analog input to the ADC.</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

|                                 | Boot Loader capabilities is not supported.                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 | <ul> <li>It is not possible to adjust the frequency of the internal calibrated RC oscillator.</li> </ul>                                                                                                                                                                                                                                                                                                                                  |

|                                 | <ul> <li>The External Memory Interface can not release any Address pins for general I/O,<br/>neither configure different wait-states to different External Memory Address<br/>sections.</li> </ul>                                                                                                                                                                                                                                        |

| Pin Descriptions                |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VCC                             | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GND                             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Port A (PA7PA0)                 | Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                                 | Port A also serves the functions of various special features of the ATmega128 as listed on page 68.                                                                                                                                                                                                                                                                                                                                       |

| Port B (PB7PB0)                 | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                                 | Port B also serves the functions of various special features of the ATmega128 as listed on page 69.                                                                                                                                                                                                                                                                                                                                       |

| Port C (PC7PC0)                 | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                 | Port C also serves the functions of special features of the ATmega128 as listed on page 72. In ATmega103 compatibility mode, Port C is output only, and the port C pins are <b>not</b> tri-stated when a reset condition becomes active.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port D (PD7PD0) | Port D is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                |

|                 | Port D also serves the functions of various special features of the ATmega128 as listed on page 73.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Port E (PE7PE0) | Port E is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                |

|                 | Port E also serves the functions of various special features of the ATmega128 as listed on page 76.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Port F (PF7PF0) | Port F serves as the analog inputs to the A/D Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.<br>Port pins can provide internal pull-up resistors (selected for each bit). The Port F output<br>buffers have symmetrical drive characteristics with both high sink and source capability.<br>As inputs, Port F pins that are externally pulled low will source current if the pull-up<br>resistors are activated. The Port F pins are tri-stated when a reset condition becomes<br>active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resis-<br>tors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even if a reset occurs. |

|                 | Port F also serves the functions of the JTAG interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | In ATmega103 compatibility mode, Port F is an input Port only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Port G (PG4PG0) | Port G is a 5-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                 |

|                 | Port G also serves the functions of various special features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | The port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | In ATmega103 compatibility mode, these pins only serves as strobes signals to the external memory as well as input to the 32 kHz oscillator, and the pins are initialized to $PG0 = 1$ , $PG1 = 1$ , and $PG2 = 0$ asynchronously when a reset condition becomes active, even if the clock is not running. PG3 and PG4 are oscillator pins.                                                                                                                                                                                                                                                                                                                             |

| RESET           | Reset input. A low level on this pin for longer than the minimum pulse length will gener-<br>ate a reset, even if the clock is not running. The minimum pulse length is given in Table<br>19 on page 46. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                                                                                                                                                                                                                                                         |

| XTAL1           | Input to the inverting oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### **XTAL2** Output from the inverting oscillator amplifier.

- AVCC This is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be connected to VCC through a low-pass filter.

- **AREF** This is the analog reference pin for the A/D Converter.

- **PEN** This is a programming enable pin for the serial programming mode. By holding this pin low during a power-on reset, the device will enter the serial programming mode. PEN has no function during normal operation.

## **Register Summary**

| Address                              | Name                          | Bit 7         | Bit 6             | Bit 5              | Bit 4       | Bit 3       | Bit 2            | Bit 1       | Bit 0       | Page           |

|--------------------------------------|-------------------------------|---------------|-------------------|--------------------|-------------|-------------|------------------|-------------|-------------|----------------|

| (\$FF)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

|                                      | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$9E)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$9D)                               | UCSR1C                        | -             | UMSEL1            | UPM11              | UPM10       | USBS1       | UCSZ11           | UCSZ10      | UCPOL1      | 185            |

| (\$9C)                               | UDR1                          | USART1 I/O E  | ata Register      |                    |             | -           |                  |             |             | 182            |

| (\$9B)                               | UCSR1A                        | RXC1          | TXC1              | UDRE1              | FE1         | DOR1        | UPE1             | U2X1        | MPCM1       | 183            |

| (\$9A)                               | UCSR1B                        | RXCIE1        | TXCIE1            | UDRIE1             | RXEN1       | TXEN1       | UCSZ12           | RXB81       | TXB81       | 184            |

| (\$99)                               | UBRR1L                        | USART1 Bau    | Rate Register L   | ow                 | 1           | 1           |                  |             |             | 186            |

| (\$98)                               | UBRR1H                        | -             | -                 | -                  | -           | USART1 Baud | Rate Register Hi | igh         |             | 186            |

| (\$97)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$96)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$95)                               | UCSR0C                        | -             | UMSEL0            | UPM01              | UPM00       | USBS0       | UCSZ01           | UCSZ00      | UCPOL0      | 185            |

| (\$94)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$93)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$92)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$91)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           | 100            |

| (\$90)                               | UBRR0H                        | -             | -                 | -                  | -           | USAR10 Baud | Rate Register Hi | Ĭ           |             | 186            |

| (\$8F)<br>(\$8E)                     | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$8E)<br>(\$8D)                     | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$8D)<br>(\$8C)                     | Reserved<br>TCCR3C            | -<br>FOC3A    | -<br>FOC3B        | -<br>FOC3C         | -           | -           | -                | -           | -           | 132            |

| (\$8C)<br>(\$8B)                     | TCCR3C<br>TCCR3A              | COM3A1        | COM3A0            | COM3B1             | -<br>COM3B0 | -<br>COM3C1 | -<br>COM3C0      | -<br>WGM31  | -<br>WGM30  | 132            |

| (\$8B)<br>(\$8A)                     | TCCR3A<br>TCCR3B              | ICNC3         | ICES3             | CONBL              | WGM33       | WGM32       | CS32             | CS31        | CS30        | 127            |

| (\$89)                               | TCCR3B<br>TCNT3H              |               | 3 - Counter Regis | ster High Byte     | W CIVISS    | WGIVI32     | 0332             | 0331        | 0000        | 130            |

| (\$88)                               | TCNT3L                        |               | 3 - Counter Regis |                    |             |             |                  |             |             | 132            |

| (\$88)                               | OCR3AH                        |               | *                 | are Register A Hid | nh Byte     |             |                  |             |             | 133            |

| (\$86)                               | OCR3AL                        |               |                   | are Register A Lo  | , ,         |             |                  |             |             | 133            |

| (\$85)                               | OCR3BH                        |               |                   | are Register B Hig |             |             |                  |             |             | 133            |

| (\$84)                               | OCR3BL                        |               | · · · ·           | are Register B Lo  |             |             |                  |             |             | 133            |

| (\$83)                               | OCR3CH                        |               | · · · ·           | are Register C Hig |             |             |                  |             |             | 133            |

| (\$82)                               | OCR3CL                        |               |                   | are Register C Lo  |             |             |                  |             |             | 133            |

| (\$81)                               | ICR3H                         |               | · · ·             | Register High By   |             |             |                  |             |             | 134            |

| (\$80)                               | ICR3L                         |               |                   | Register Low By    |             |             |                  |             |             | 134            |

| (\$7F)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$7E)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$7D)                               | ETIMSK                        | -             | -                 | TICIE3             | OCIE3A      | OCIE3B      | TOIE3            | OCIE3C      | OCIE1C      | 135            |

| (\$7C)                               | ETIFR                         | -             | -                 | ICF3               | OCF3A       | OCF3B       | TOV3             | OCF3C       | OCF1C       | 136            |

| (\$7B)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$7A)                               | TCCR1C                        | FOC1A         | FOC1B             | FOC1C              | -           | -           | -                | -           | -           | 131            |

| (\$79)                               | OCR1CH                        | Timer/Counter | 1 - Output Comp   | are Register C Hig | gh Byte     |             |                  |             |             | 133            |

| (\$78)                               | OCR1CL                        | Timer/Counter | 1 - Output Comp   | are Register C Lo  | w Byte      | 1           | 1                |             |             | 133            |

| (\$77)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$76)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$75)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           |                |

| (\$74)                               | TWCR                          | TWINT         | TWEA              | TWSTA              | TWSTO       | TWWC        | TWEN             | -           | TWIE        | 198            |

| (\$73)                               | TWDR                          |               | nterface Data Re  | Ť                  |             |             |                  |             |             | 199            |

| (\$72)                               | TWAR                          | TWA6          | TWA5              | TWA4               | TWA3        | TWA2        | TWA1             | TWA0        | TWGCE       | 200            |

| (\$671                               | TWSR                          | TWS7          | TWS6              | TWS5               | TWS4        | TWS3        | -                | TWPS1       | TWPS0       | 199            |

| (\$70)                               | TWBR                          |               | nterface Bit Rate | Register           |             |             |                  |             |             | 197            |

| (\$6F)                               | OSCCAL                        |               | bration Register  |                    |             |             |                  |             |             | 38             |

| (\$6E)                               | Reserved                      | -             | -                 | -                  | -           | -           | -                | -           | -           | 00             |

| (\$6D)                               | XMCRA                         | -             | SRL2              | SRL1               | SRL0        | SRW01       | SRW00            | SRW11       | VMM         | 29             |

| (\$6C)<br>(\$6B)                     | XMCRB                         | XMBK          | -                 | -                  | -           | -           | XMM2<br>-        | XMM1<br>-   | XMM0        | 31             |

|                                      | Reserved                      |               | -<br>ISC30        | -                  | -           | -           |                  |             |             | 94             |

| (\$6A)<br>(\$69)                     | EICRA                         | ISC31         | -                 | ISC21              | ISC20       | ISC11       | ISC10            | ISC01       | ISC00       | 84             |

| (403)                                | Reserved<br>SPMCSR            | -<br>SPMIE    | -<br>RWWSB        | -                  | -<br>RWWSRE | -<br>BLBSET | -<br>PGWRT       | -<br>PGERS  | -<br>SPMEN  | 270            |

|                                      |                               |               |                   | -                  |             |             | -                |             |             | 210            |

| (\$68)                               |                               |               |                   | -                  | -           | -           | -                | -           | -           |                |

| (\$68)<br>(\$67)                     | Reserved                      | -             |                   | 1                  | -           | -           |                  | -           |             |                |

| (\$68)<br>(\$67)<br>(\$66)           | Reserved<br>Reserved          | -             | -                 | -                  | -<br>POBTG4 | -<br>POBTG3 | -<br>POBTG2      | -<br>PORTG1 | -<br>POBTG0 | 83             |

| (\$68)<br>(\$67)<br>(\$66)<br>(\$65) | Reserved<br>Reserved<br>PORTG | -             | -                 | -                  | PORTG4      | PORTG3      | PORTG2           | PORTG1      | PORTG0      | 83             |

| (\$68)<br>(\$67)<br>(\$66)           | Reserved<br>Reserved          | -             | -                 | -                  |             |             |                  |             |             | 83<br>83<br>83 |

# Register Summary (Continued)

|                                                                                                                                     |                                                                       |                                                                                      |                                                                                                   |                                       |                             |                       | -                      |                     |                        | _                                             |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|-----------------------|------------------------|---------------------|------------------------|-----------------------------------------------|

| Address                                                                                                                             | Name                                                                  | Bit 7                                                                                | Bit 6                                                                                             | Bit 5                                 | Bit 4                       | Bit 3                 | Bit 2                  | Bit 1               | Bit 0                  | Page                                          |

| (\$61)                                                                                                                              | DDRF                                                                  | DDF7                                                                                 | DDF6                                                                                              | DDF5                                  | DDF4                        | DDF3                  | DDF2                   | DDF1                | DDF0                   | 83                                            |

| (\$60)                                                                                                                              | Reserved                                                              | -                                                                                    | -                                                                                                 | -                                     | -                           | -                     | -                      | -                   | -                      |                                               |

| \$3F (\$5F)                                                                                                                         | SREG                                                                  | 1                                                                                    | Т                                                                                                 | н                                     | S                           | V                     | N                      | Z                   | С                      | 9                                             |

| \$3E (\$5E)                                                                                                                         | SPH                                                                   | SP15                                                                                 | SP14                                                                                              | SP13                                  | SP12                        | SP11                  | SP10                   | SP9                 | SP8                    | 12                                            |

| \$3D (\$5D)                                                                                                                         | SPL                                                                   | SP7                                                                                  | SP6                                                                                               | SP5                                   | SP4                         | SP3                   | SP2                    | SP1                 | SP0                    | 12                                            |

| \$3C (\$5C)                                                                                                                         | XDIV                                                                  | XDIVEN                                                                               | XDIV6                                                                                             | XDIV5                                 | XDIV4                       | XDIV3                 | XDIV2                  | XDIV1               | XDIV0                  | 39                                            |

| \$3B (\$5B)                                                                                                                         | RAMPZ                                                                 | -                                                                                    | -                                                                                                 | -                                     | -                           | -                     | -                      | -                   | RAMPZ0                 | 12                                            |

| \$3A (\$5A)                                                                                                                         | EICRB                                                                 | ISC71                                                                                | ISC70                                                                                             | ISC61                                 | ISC60                       | ISC51                 | ISC50                  | ISC41               | ISC40                  | 85                                            |

| \$39 (\$59)                                                                                                                         | EIMSK                                                                 | INT7                                                                                 | INT6                                                                                              | INT5                                  | INT4                        | INT3                  | INT2                   | INT1                | INT0                   | 86                                            |

| \$38 (\$58)                                                                                                                         | EIFR                                                                  | INTF7                                                                                | INTF6                                                                                             | INTF5                                 | INTF4                       | INTF3                 | INTF                   | INTF1               | INTF0                  | 86                                            |

| \$37 (\$57)                                                                                                                         | TIMSK                                                                 | OCIE2                                                                                | TOIE2                                                                                             | TICIE1                                | OCIE1A                      | OCIE1B                | TOIE1                  | OCIE0               | TOIE0                  | 103, 134, 153                                 |

| \$36 (\$56)                                                                                                                         | TIFR                                                                  | OCF2                                                                                 | TOV2                                                                                              | ICF1                                  | OCF1A                       | OCF1B                 | TOV1                   | OCF0                | TOV0                   | 103, 136, 154                                 |

| \$35 (\$55)                                                                                                                         | MCUCR                                                                 | SRE                                                                                  | SRW10                                                                                             | SE                                    | SM1                         | SMO                   | SM2                    | IVSEL               | IVCE                   | 29, 41, 58                                    |

| \$34 (\$54)                                                                                                                         | MCUCSR                                                                | JTD                                                                                  | -                                                                                                 | -                                     | JTRF                        | WDRF                  | BORF                   | EXTRF               | PORF                   | 49, 246                                       |

| \$33 (\$53)                                                                                                                         | TCCR0                                                                 | FOC0                                                                                 | WGM00                                                                                             | COM01                                 | COM00                       | WGM01                 | CS02                   | CS01                | CS00                   | 98                                            |

| \$32 (\$52)                                                                                                                         | TCNT0                                                                 | Timer/Counte                                                                         | 1 1                                                                                               |                                       |                             |                       |                        |                     |                        | 100                                           |

| \$31 (\$51)                                                                                                                         | OCR0                                                                  | Timer/Counte                                                                         | r0 Output Compa                                                                                   | re Register                           |                             |                       |                        |                     |                        | 100                                           |

| \$30 (\$50)                                                                                                                         | ASSR                                                                  | -                                                                                    | -                                                                                                 | -                                     | -                           | AS0                   | TCN0UB                 | OCROUB              | TCR0UB                 | 101                                           |

| \$2F (\$4F)                                                                                                                         | TCCR1A                                                                | COM1A1                                                                               | COM1A0                                                                                            | COM1B1                                | COM1B0                      | COM1C1                | COM1C0                 | WGM11               | WGM10                  | 127                                           |

| \$2E (\$4E)                                                                                                                         | TCCR1B                                                                | ICNC1                                                                                | ICES1                                                                                             | -                                     | WGM13                       | WGM12                 | CS12                   | CS11                | CS10                   | 130                                           |

| \$2D (\$4D)                                                                                                                         | TCNT1H                                                                |                                                                                      | 1 - Counter Regi                                                                                  |                                       |                             |                       |                        |                     |                        | 132                                           |

| \$2C (\$4C)                                                                                                                         | TCNT1L                                                                |                                                                                      | 1 - Counter Regi                                                                                  | ,                                     |                             |                       |                        |                     |                        | 132                                           |

| \$2B (\$4B)                                                                                                                         | OCR1AH                                                                |                                                                                      |                                                                                                   | are Register A Hig                    |                             |                       |                        |                     |                        | 133                                           |

| \$2A (\$4A)                                                                                                                         | OCR1AL                                                                |                                                                                      |                                                                                                   | are Register A Lov                    |                             |                       |                        |                     |                        | 133                                           |

| \$29 (\$49)                                                                                                                         | OCR1BH                                                                |                                                                                      |                                                                                                   | are Register B Hig                    |                             |                       |                        |                     |                        | 133                                           |

| \$28 (\$48)                                                                                                                         | OCR1BL                                                                |                                                                                      |                                                                                                   | are Register B Lov                    |                             |                       |                        |                     |                        | 133                                           |

| \$27 (\$47)                                                                                                                         | ICR1H                                                                 |                                                                                      |                                                                                                   | Register High By                      |                             |                       |                        |                     |                        | 134                                           |

| \$26 (\$46)                                                                                                                         | ICR1L                                                                 |                                                                                      |                                                                                                   | Register Low Byt                      |                             |                       | 1                      |                     |                        | 134                                           |

| \$25 (\$45)                                                                                                                         | TCCR2                                                                 | FOC2                                                                                 | WGM20                                                                                             | COM21                                 | COM20                       | WGM21                 | CS22                   | CS21                | CS20                   | 151                                           |

| \$24 (\$44)                                                                                                                         | TCNT2                                                                 | Timer/Counter                                                                        |                                                                                                   |                                       |                             |                       |                        |                     |                        | 153                                           |

| \$23 (\$43)                                                                                                                         | OCR2                                                                  |                                                                                      | 2 Output Compar                                                                                   | e Register                            | 1                           |                       | 1                      |                     |                        | 153                                           |

| \$22 (\$42)                                                                                                                         | OCDR                                                                  | IDRD/<br>OCDR7                                                                       | OCDR6                                                                                             | OCDR5                                 | OCDR4                       | OCDR3                 | OCDR2                  | OCDR1               | OCDR0                  | 242                                           |

| \$21 (\$41)                                                                                                                         | WDTCR                                                                 | -                                                                                    | -                                                                                                 | _                                     | WDCE                        | WDE                   | WDP2                   | WDP1                | WDP0                   | 51                                            |

| \$20 (\$40)                                                                                                                         | SFIOR                                                                 | TSM                                                                                  | -                                                                                                 | _                                     | ADHSM                       | ACME                  | PUD                    | PSR0                | PSR321                 | 67, 104, 139, 237                             |

| \$1F (\$3F)                                                                                                                         | EEARH                                                                 | -                                                                                    | -                                                                                                 | -                                     | -                           |                       |                        | ess Register High   |                        | 19                                            |

| \$1E (\$3E)                                                                                                                         | EEARL                                                                 | EEPROM Add                                                                           | Iress Register Lov                                                                                | v Bvte                                |                             |                       |                        | eee riegieter riigi |                        | 19                                            |

| \$1D (\$3D)                                                                                                                         | EEDR                                                                  | EEPROM Data                                                                          |                                                                                                   |                                       |                             |                       |                        |                     |                        | 20                                            |

| \$1C (\$3C)                                                                                                                         | EECR                                                                  | -                                                                                    | -                                                                                                 | -                                     | -                           | EERIE                 | EEMWE                  | EEWE                | EERE                   | 20                                            |

| \$1B (\$3B)                                                                                                                         | PORTA                                                                 | PORTA7                                                                               | PORTA6                                                                                            | PORTA5                                | PORTA4                      | PORTA3                | PORTA2                 | PORTA1              | PORTA0                 | 81                                            |

| \$1A (\$3A)                                                                                                                         | DDRA                                                                  | DDA7                                                                                 | DDA6                                                                                              | DDA5                                  | DDA4                        | DDA3                  | DDA2                   | DDA1                | DDA0                   | 81                                            |

| \$19 (\$39)                                                                                                                         | PINA                                                                  | PINA7                                                                                | PINA6                                                                                             | PINA5                                 | PINA4                       | PINA3                 | PINA2                  | PINA1               | PINA0                  | 81                                            |

| \$18 (\$38)                                                                                                                         | PORTB                                                                 | PORTB7                                                                               | PORTB6                                                                                            | PORTB5                                | PORTB4                      | PORTB3                | PORTB2                 | PORTB1              | PORTB0                 | 81                                            |

| \$17 (\$37)                                                                                                                         | DDRB                                                                  | DDB7                                                                                 | DDB6                                                                                              | DDB5                                  | DDB4                        | DDB3                  | DDB2                   | DDB1                | DDB0                   | 81                                            |

| \$16 (\$36)                                                                                                                         | PINB                                                                  | PINB7                                                                                | PINB6                                                                                             | PINB5                                 | PINB4                       | PINB3                 | PINB2                  | PINB1               | PINB0                  | 82                                            |

| \$15 (\$35)                                                                                                                         | PORTC                                                                 | PORTC7                                                                               | PORTC6                                                                                            | PORTC5                                | PORTC4                      | PORTC3                | PORTC2                 | PORTC1              | PORTC0                 | 82                                            |

| \$14 (\$34)                                                                                                                         | DDRC                                                                  | DDC7                                                                                 | DDC6                                                                                              | DDC5                                  | DDC4                        | DDC3                  | DDC2                   | DDC1                | DDC0                   | 82                                            |

| \$13 (\$33)                                                                                                                         | PINC                                                                  | PINC7                                                                                | PINC6                                                                                             | PINC5                                 | PINC4                       | PINC3                 | PINC2                  | PINC1               | PINC0                  | 82                                            |

| \$12 (\$32)                                                                                                                         | PORTD                                                                 | PORTD7                                                                               | PORTD6                                                                                            | PORTD5                                | PORTD4                      | PORTD3                | PORTD2                 | PORTD1              | PORTD0                 | 82                                            |

| \$11 (\$31)                                                                                                                         | DDRD                                                                  | DDD7                                                                                 | DDD6                                                                                              | DDD5                                  | DDD4                        | DDD3                  | DDD2                   | DDD1                | DDD0                   | 82                                            |

| \$10 (\$30)                                                                                                                         | PIND                                                                  | PIND7                                                                                | PIND6                                                                                             | PIND5                                 | PIND4                       | PIND3                 | PIND2                  | PIND1               | PIND0                  | 82                                            |

| \$0F (\$2F)                                                                                                                         | SPDR                                                                  | SPI Data Reg                                                                         |                                                                                                   |                                       |                             |                       |                        |                     |                        | 163                                           |

|                                                                                                                                     | SPSR                                                                  | SPIF                                                                                 | WCOL                                                                                              | -                                     | -                           | -                     | -                      | -                   | SPI2X                  | 162                                           |

| \$0E (\$2E)                                                                                                                         |                                                                       |                                                                                      |                                                                                                   | DORD                                  | MSTR                        | CPOL                  | СРНА                   | SPR1                | SPR0                   | 161                                           |

| \$0E (\$2E)<br>\$0D (\$2D)                                                                                                          | SPCR                                                                  | SPIE                                                                                 | SPE                                                                                               |                                       |                             |                       |                        |                     |                        | 182                                           |

| \$0D (\$2D)                                                                                                                         | SPCR<br>UDR0                                                          | SPIE<br>USART0 I/O I                                                                 |                                                                                                   | Donib                                 |                             |                       |                        |                     |                        |                                               |

| \$0D (\$2D)<br>\$0C (\$2C)                                                                                                          | UDR0                                                                  | USART0 I/O I                                                                         | Data Register                                                                                     | 1                                     |                             | DOR0                  | UPE0                   | U2X0                | MPCM0                  |                                               |

| \$0D (\$2D)<br>\$0C (\$2C)<br>\$0B (\$2B)                                                                                           | UDR0<br>UCSR0A                                                        | USART0 I/O I<br>RXC0                                                                 | Data Register<br>TXC0                                                                             | UDRE0                                 | FE0                         | DOR0<br>TXEN0         | UPE0<br>UCSZ02         | U2X0<br>RXB80       | MPCM0<br>TXB80         | 183                                           |

| \$0D (\$2D)<br>\$0C (\$2C)<br>\$0B (\$2B)<br>\$0A (\$2A)                                                                            | UDR0<br>UCSR0A<br>UCSR0B                                              | USART0 I/O I<br>RXC0<br>RXCIE0                                                       | Data Register<br>TXC0<br>TXCIE0                                                                   | UDRE0<br>UDRIE0                       |                             | DOR0<br>TXEN0         | UPE0<br>UCSZ02         | U2X0<br>RXB80       | MPCM0<br>TXB80         | 183<br>184                                    |